34 www.xilinx.com Spartan-6 FPGA PCB Design and Pin Planning

UG393 (v1.1) April 29, 2010

Chapter 2: Power Distribution System

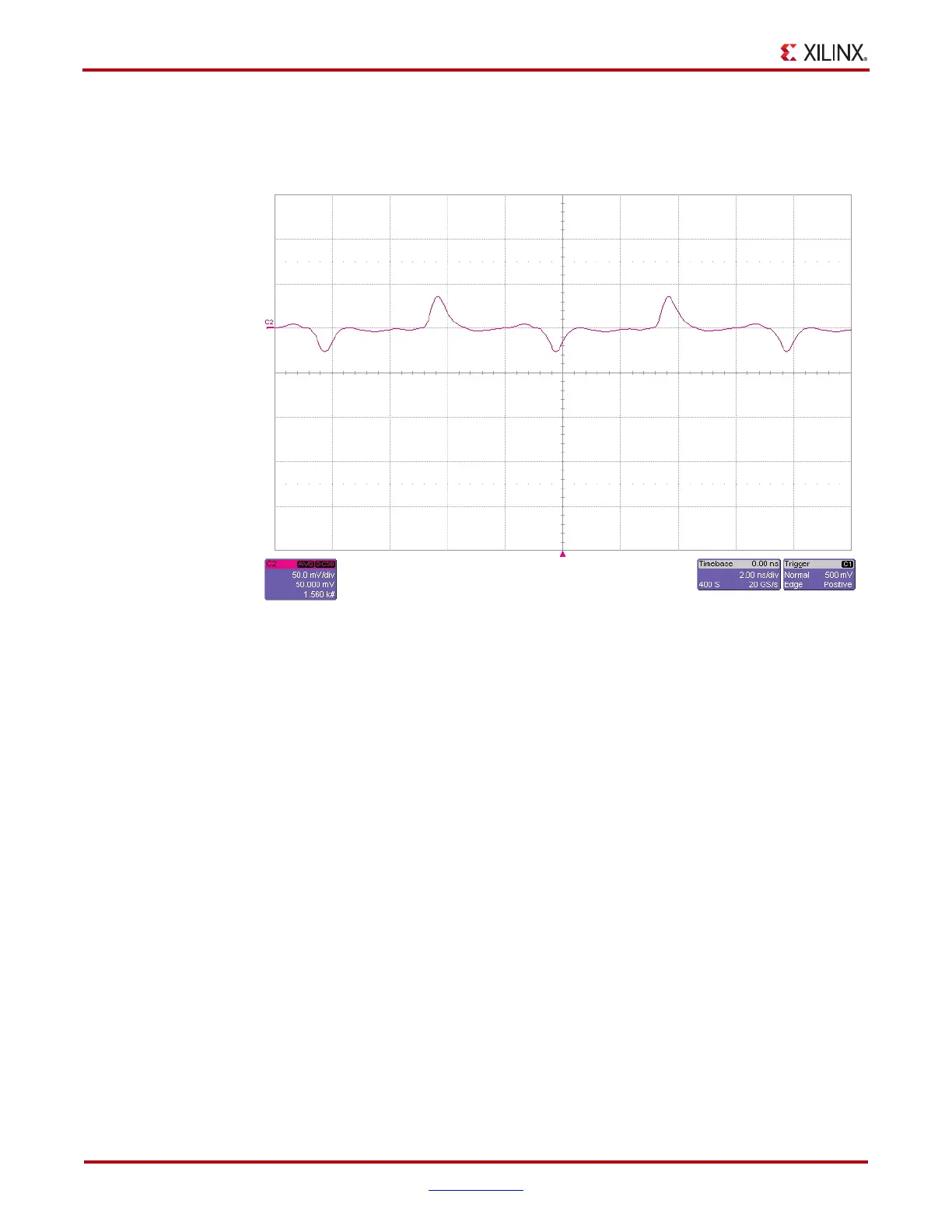

Figure 2-9 shows an averaged noise measurement taken at the V

CCO

pins of a sample

design. In this case, the trigger was the clock for an I/O bus interface sending a 1-0-1-0

pattern at 250 Mb/s.

X-Ref Target - Figure 2-9

Figure 2-9: Averaged Measurement of V

CCO

Supply with Multiple I/O Sending

Patterns at 250 Mb/s

ug393_c2_09_091809

Loading...

Loading...