52 www.xilinx.com Spartan-6 FPGA PCB Design and Pin Planning

UG393 (v1.1) April 29, 2010

Chapter 5: Design of Transitions for High-Speed Signals

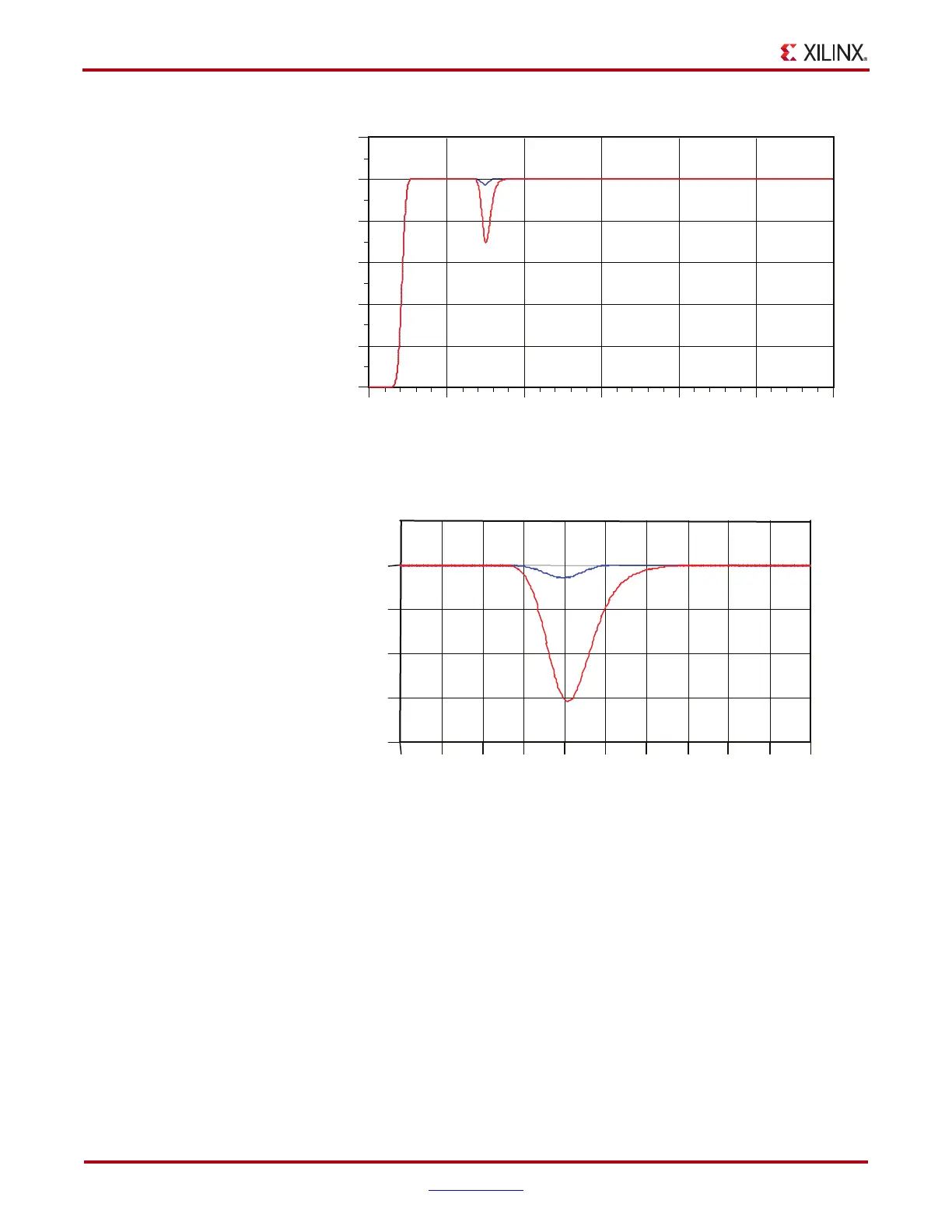

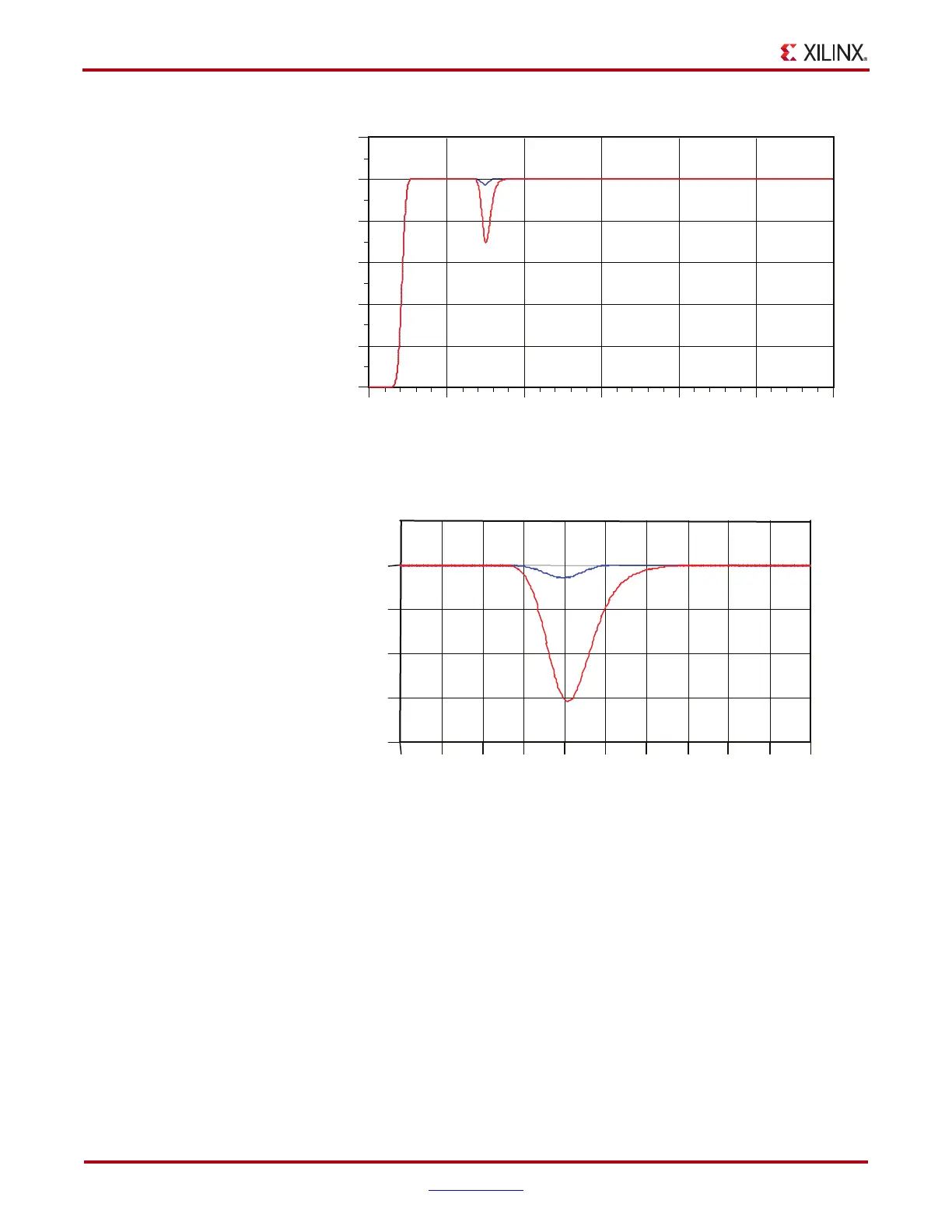

As shown from Figure 5-11 and Figure 5-12, clearing the ground plane under SMT pads

yields a significant improvement in the performance of an SMT pad transition. Excess

capacitance is reduced by 15x, and return loss is improved by 20 dB.

X-Ref Target - Figure 5-9

Figure 5-9: TDR Results Comparing 0402 Pad Structures

X-Ref Target - Figure 5-10

Figure 5-10: TDR Results Comparing 0402 Pad Structures

0

100

200

300

400

500

600

0.0 0.5 1.0 1.5

Time, ns

2.0 2.5 3.0

VtdrPlaneCleared, mV

VtdrPlaneNotCleared, mV

UG393_c5_09_091809

0.60 0.65 0.70 0.75 0.800.85 0.90 0.95 1.000.55 1.05

350

400

450

500

300

550

Time, ns

VtdrPlaneNotCleared, mV

VtdrPlaneCleared, mV

UG393_c5_10_091809

Loading...

Loading...