58 www.xilinx.com Spartan-6 FPGA PCB Design and Pin Planning

UG393 (v1.1) April 29, 2010

Chapter 5: Design of Transitions for High-Speed Signals

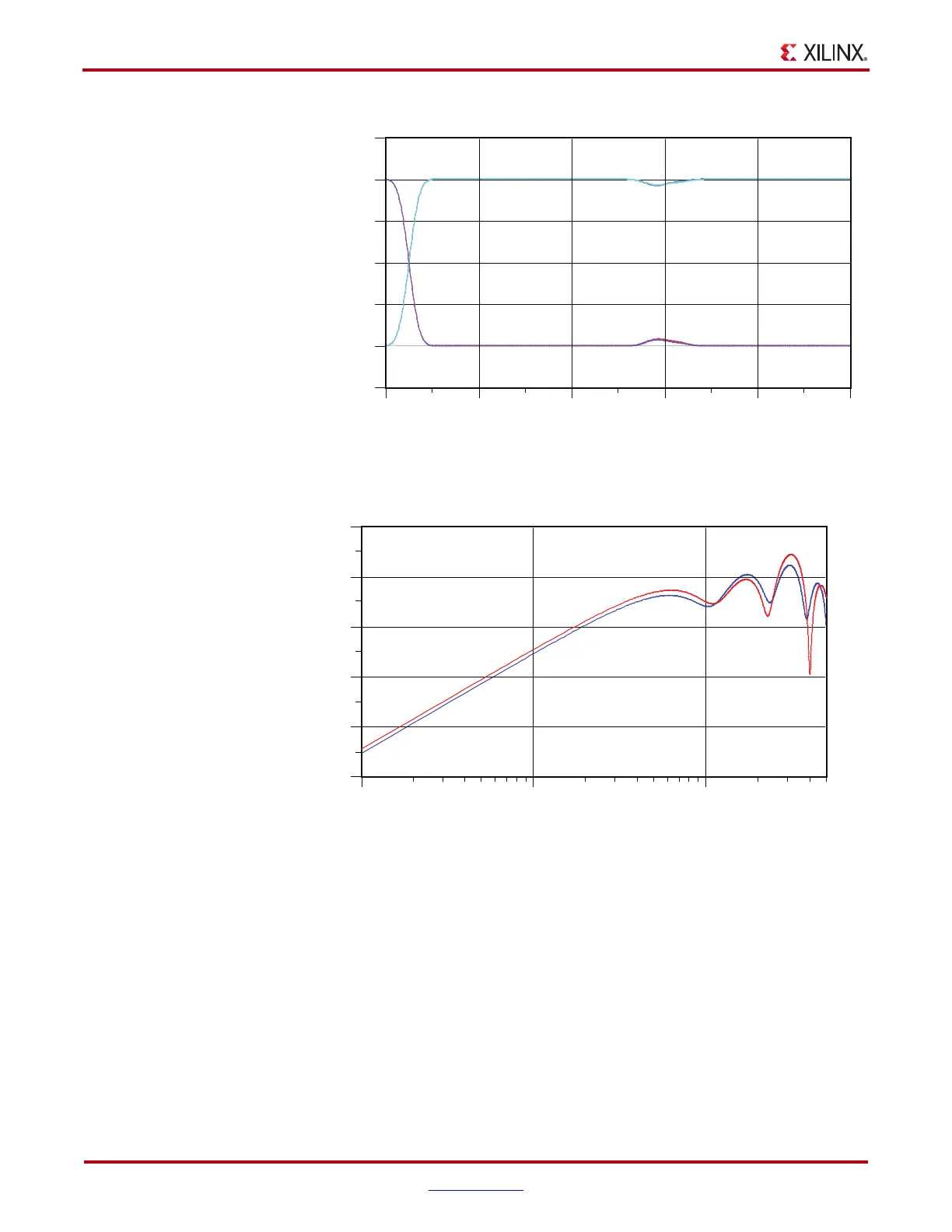

X-Ref Target - Figure 5-17

Figure 5-17: Simulated TDR of 45 Degree Bends with Jog-Outs

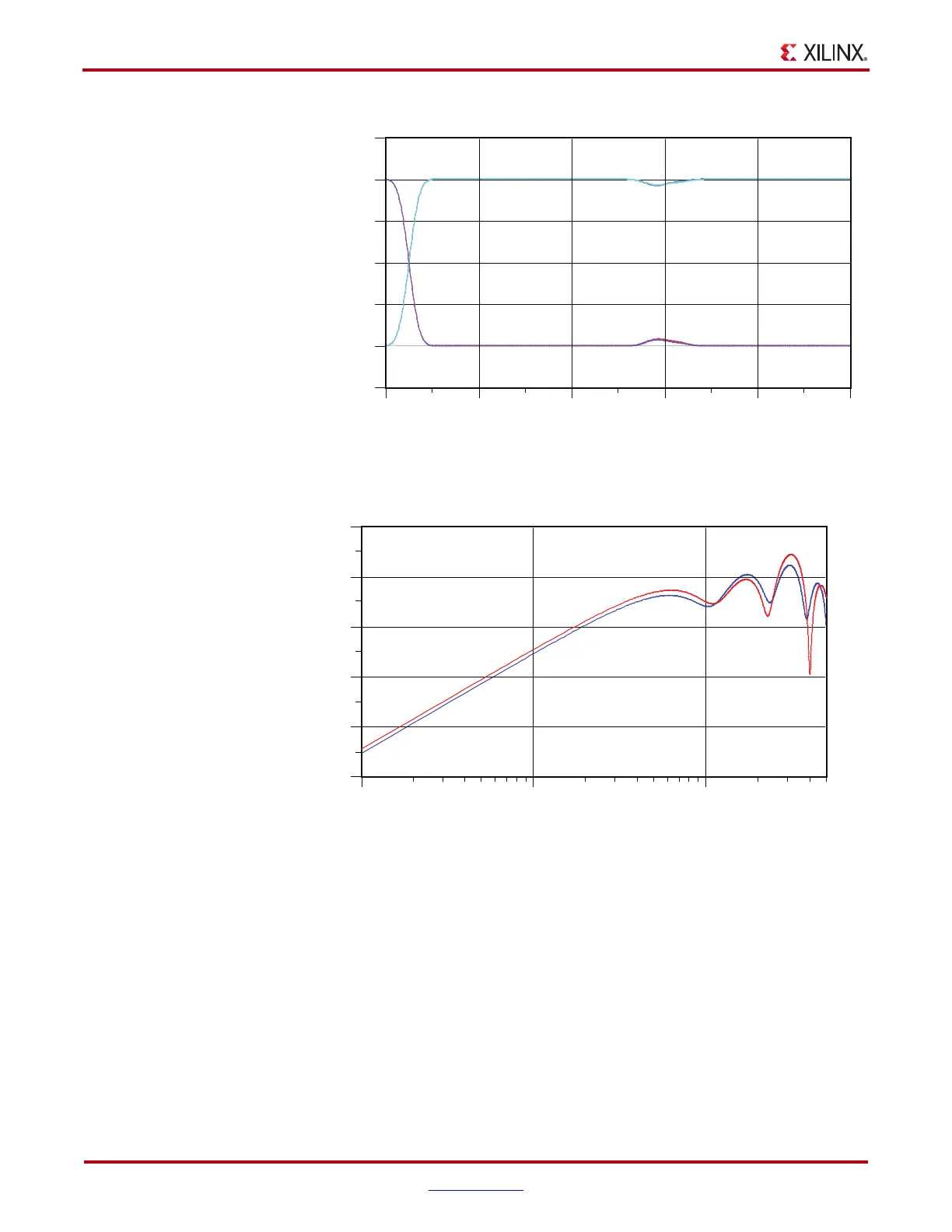

X-Ref Target - Figure 5-18

Figure 5-18: Simulated TDR of 45 Degree Bends with Jog-Outs

2.5

2.0

1.5

1.0

0.5

0.0

-0.5

0.0 0.2 0.4 0.6

Time, ns

0.8 1.0

vtdr_dutp, V

vtdr_dutn, V

vtdr_dutn2, V

vtdr_dutp2, V

UG393_c5_17_091809

-10

-20

-30

-40

-50

-60

1E8 1E9

Frequency, Hz

1E10

5E10

dB(Sdd11x)

dB(Sdd11)

UG393_c5_18_091809

Loading...

Loading...