Spartan-6 FPGA PCB Design and Pin Planning www.xilinx.com 59

UG393 (v1.1) April 29, 2010

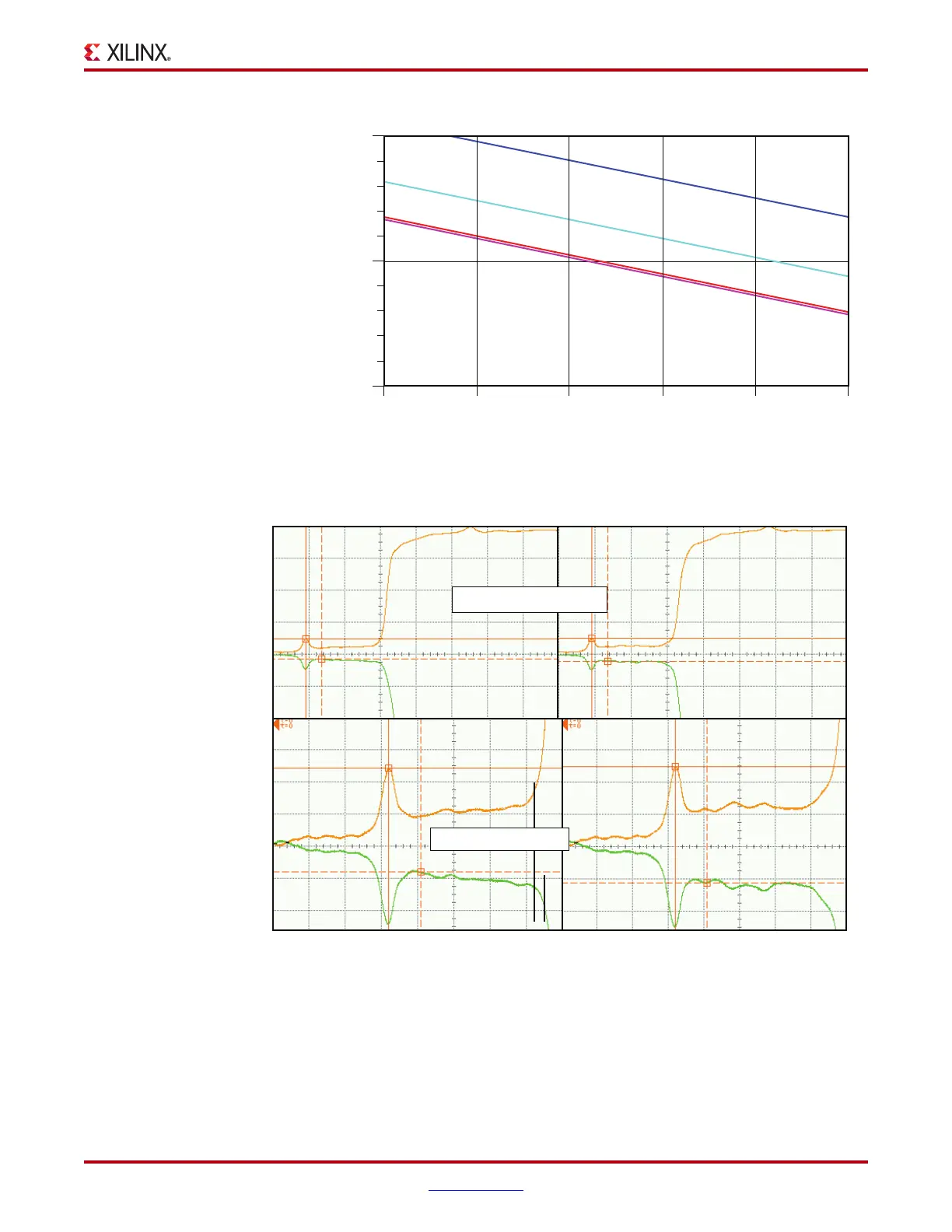

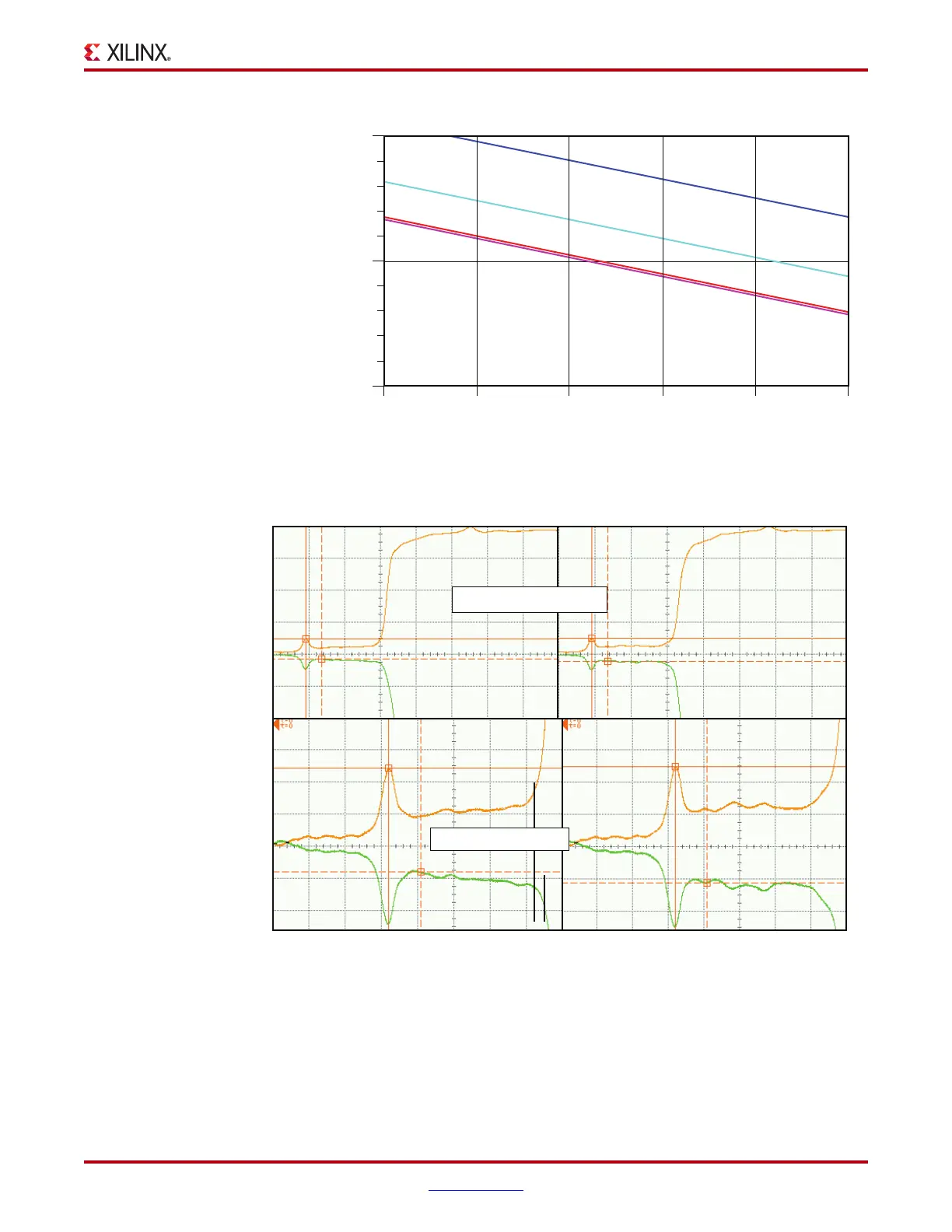

Microstrip/Stripline Bends

For wide traces, curved routing can also be helpful as shown in Figure 5-20.

X-Ref Target - Figure 5-19

Figure 5-19: Simulated Phase Response of 45 Degree Bends with Jog-Outs

X-Ref Target - Figure 5-20

Figure 5-20: Measured TDR of 45 Degree Bends with and without Jog-Outs

-75

-76

-77

4.95

Frequency, GHz

5.00

Phase(S(4,2))

Phase(S(3,1))

Phase(S(8,6))

Phase(S(7,5))

UG393_c5_19_091809

UG393_c5_20_091809

No Jog-outs

No Jog-outs

With Jog-outs

With Jog-outs

Turns & Jog-outs

Turns

Skew

50 mV, 200 ps Per Div.

10 mV, 100 ps Per Div.

Loading...

Loading...