MC96F6432

114 June 22, 2018 Ver. 2.9

11.2.3 Register Map

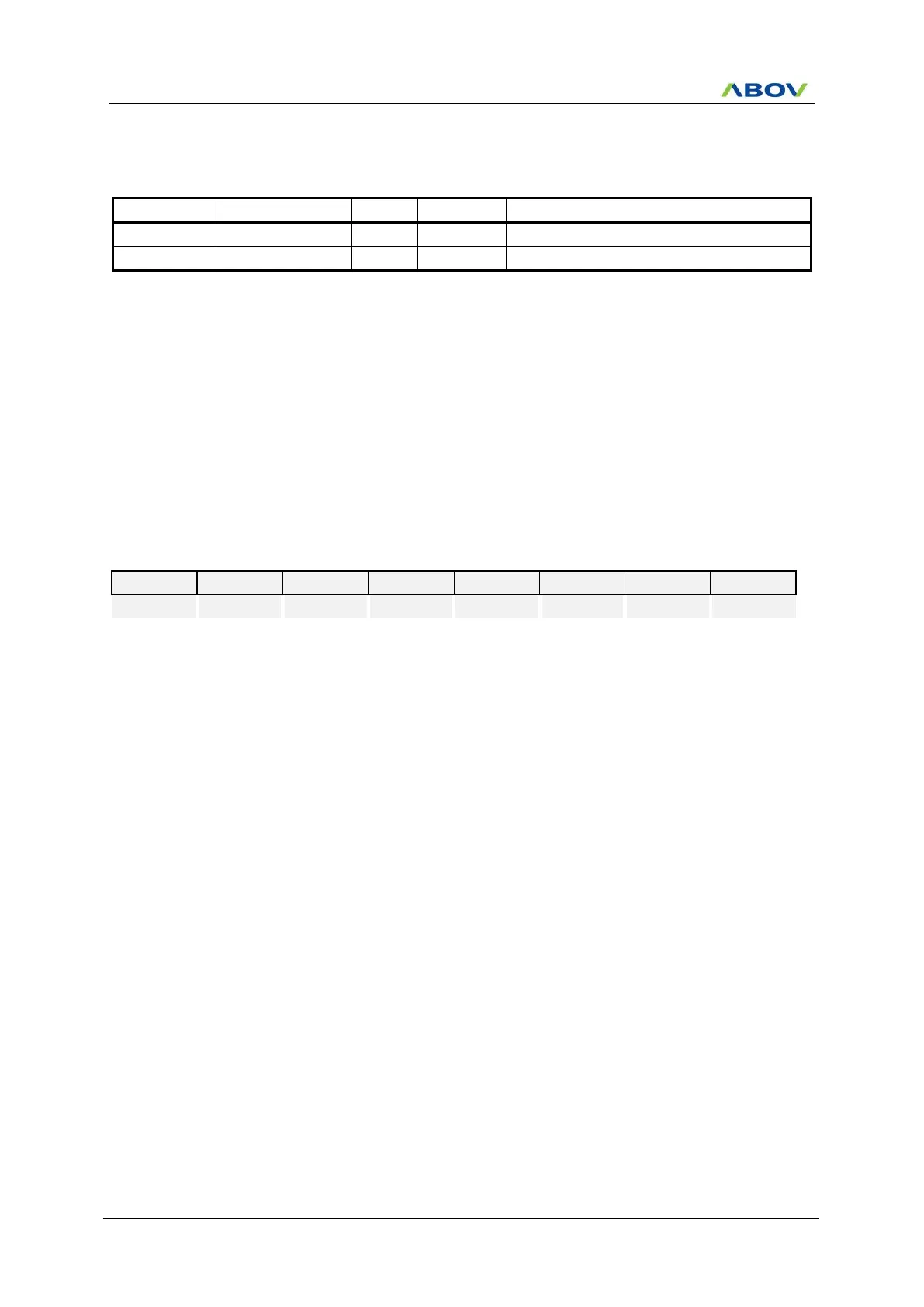

Table 11-2 Basic Interval Timer Register Map

Basic Interval Timer Counter Register

Basic Interval Timer Control Register

11.2.4 Basic Interval Timer Register Description

The basic interval timer register consists of basic interval timer counter register (BITCNT) and basic interval

timer control register (BITCR). If BCLR bit is set to ‘1’, BITCNT becomes ‘0’ and then counts up. After 1 machine

cycle, BCLR bit is cleared to ‘0’ automatically.

11.2.5 Register Description for Basic Interval Timer

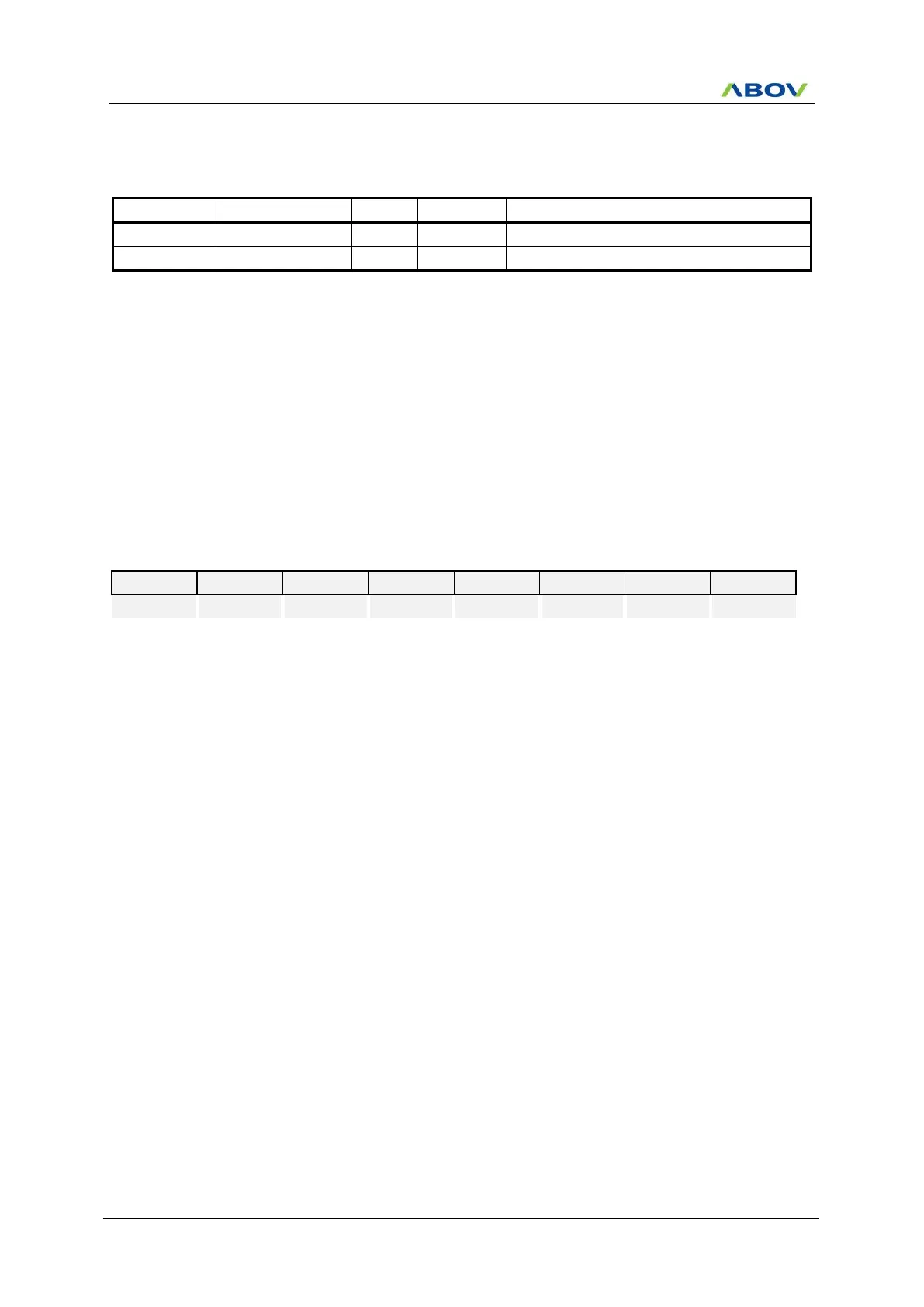

BITCNT (Basic Interval Timer Counter Register) : 8CH

Initial value : 00H

Loading...

Loading...