MC96F6432

148 June 22, 2018 Ver. 2.9

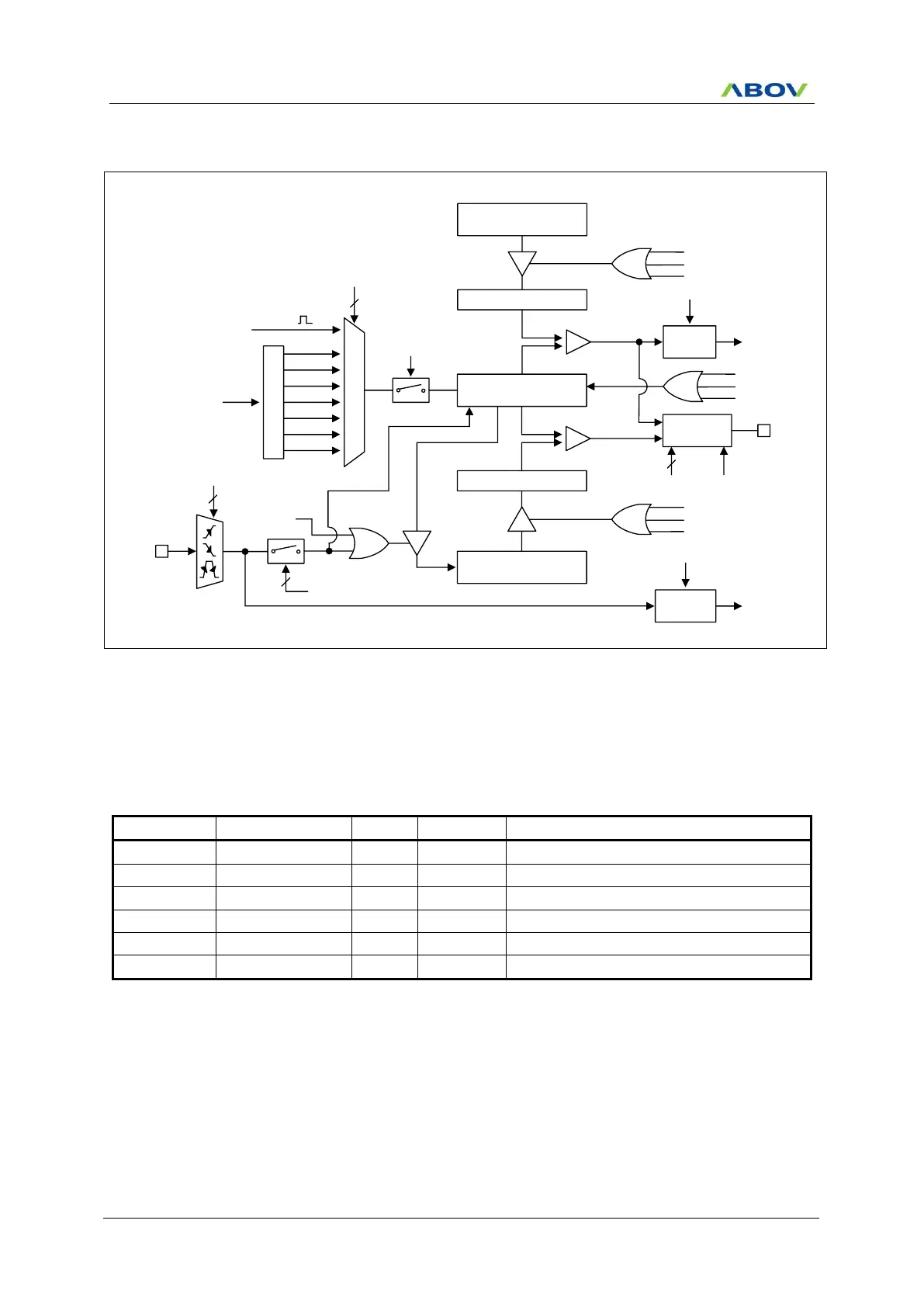

11.7.5 Block Diagram

T2MS[1:0]

T2POL

Reload

A Match

T2CC

T2EN

P

r

e

s

c

a

l

e

r

fx

M

U

X

fx/2

fx/4

fx/32

fx/128

fx/512

fx/8

fx/1

Comparator

16-bit Counter

T2CNTH/T2CNTL

16-bit B Data Register

T2BDRH/T2BDRL

Clear

B Match

Buffer Register B

Comparator

16-bit A Data Register

T2ADRH/T2ADRL

T2IFR

INT_ACK

Clear

To interrupt

block

A Match

Buffer Register A

Reload

Pulse

Generator

T2O/

PWM2O

R

EINT12

T2CNTR

T2EN

3

T2CK[2:0]

Clear

EIPOL1[7:6]

FLAG12

(EIFLAG1.3)

INT_ACK

Clear

To interrupt

block

2

2

T2MS[1:0]

2

T1 A Match

A Match

T2CC

T2EN

A Match

T2CC

T2EN

NOTE) T1 A Match is a pulse for the timer 2 clock source if it is selected.

Figure 11.29 16-Bit Timer 2 Block Diagram

11.7.6 Register Map

Table 11-10 Timer 3 Register Map

Timer 2 A Data High Register

Timer 2 A Data Low Register

Timer 2 B Data High Register

Timer 2 B Data Low Register

Timer 2 Control High Register

Timer 2 Control Low Register

Loading...

Loading...