MC96F6432

294 June 22, 2018 Ver. 2.9

13.9 Register Map

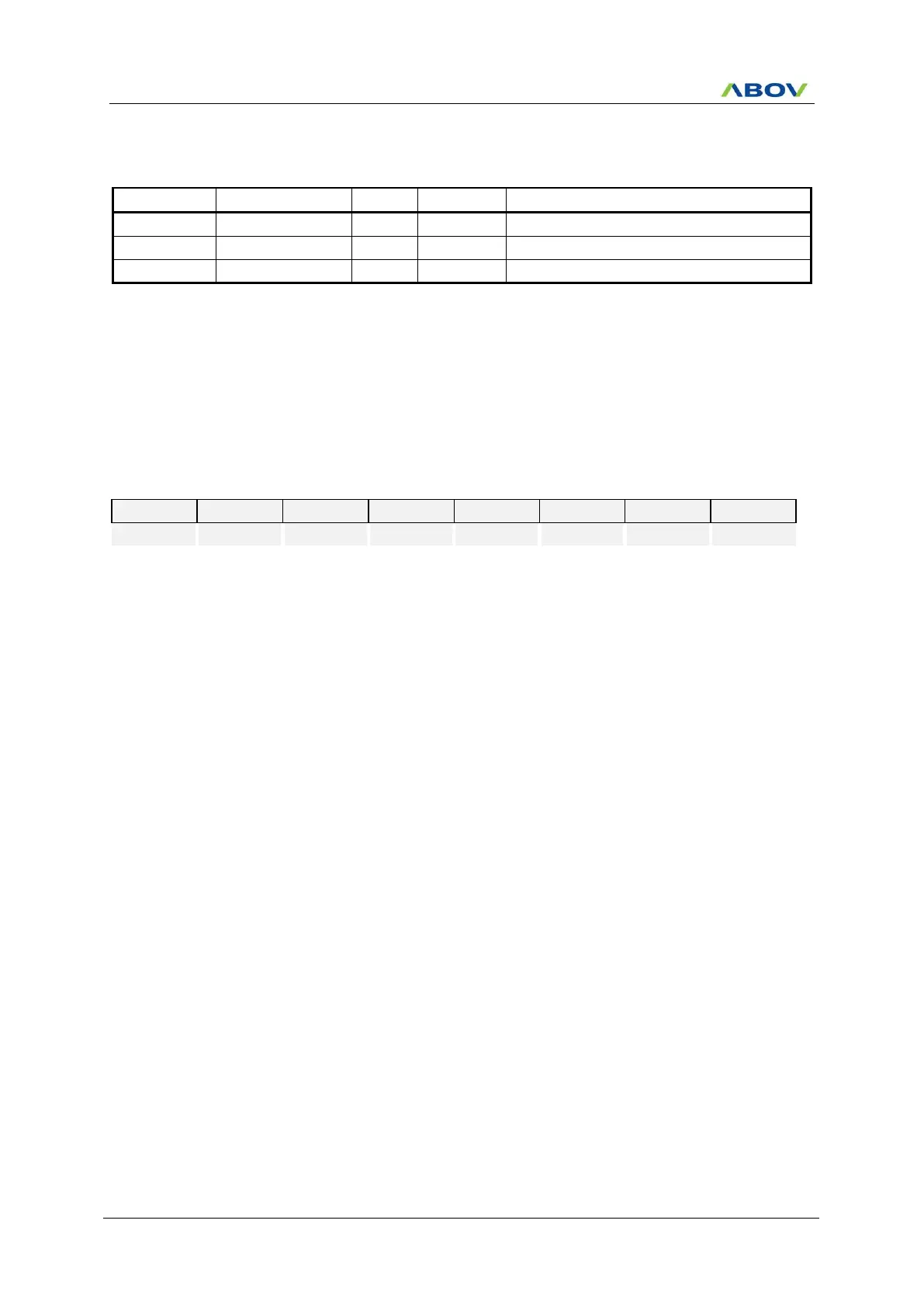

Table 13-3 Reset Operation Register Map

Low Voltage Reset Control Register

Low Voltage Indicator Control Register

13.10 Reset Operation Register Description

The reset control register consists of the reset flag register (RSTFR), low voltage reset control register (LVRCR),

and low voltage indicator control register (LVICR).

13.11 Register Description for Reset Operation

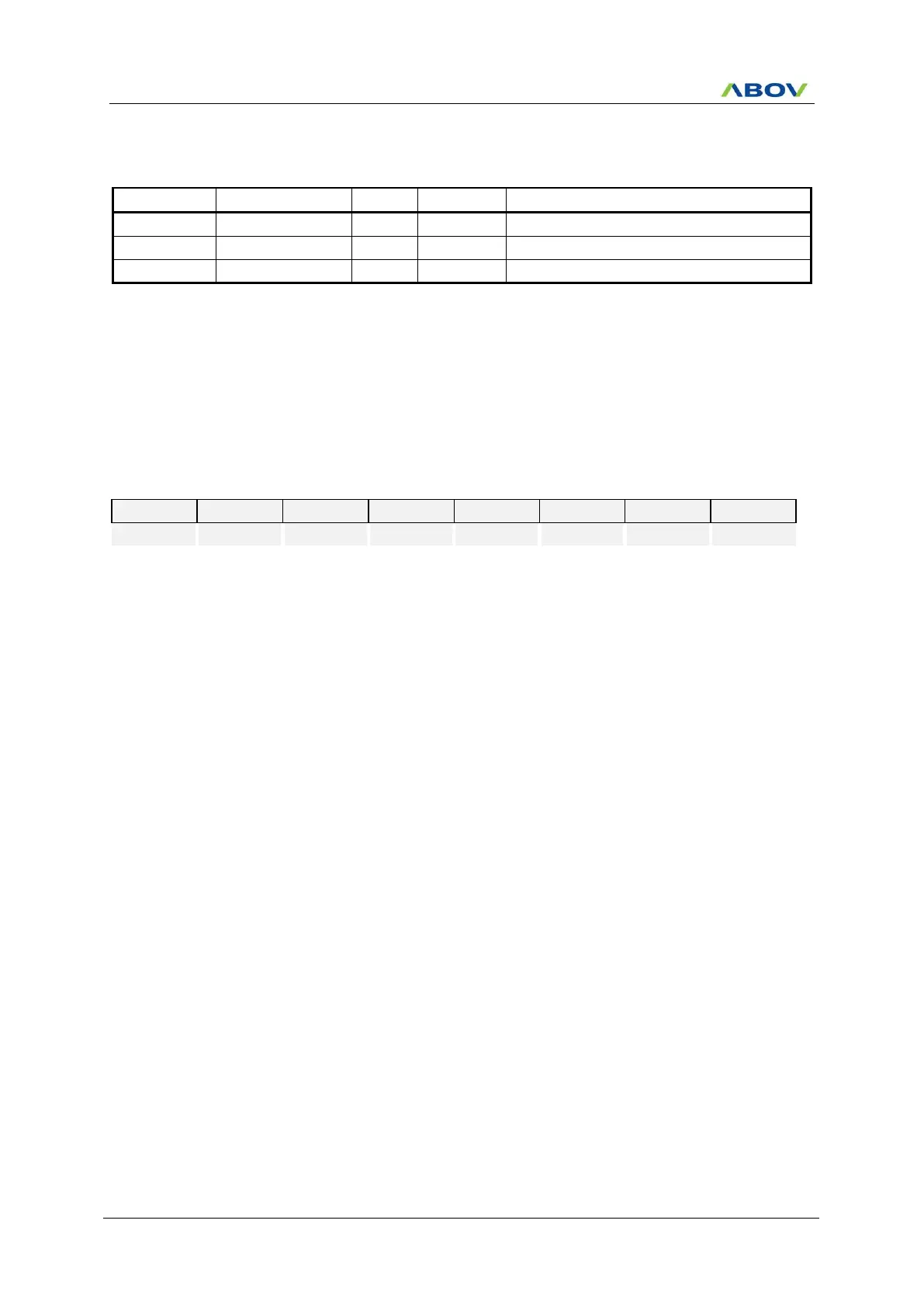

RSTFR (Reset Flag Register) : E8H

Initial value : 80H

Power-On Reset flag bit. The bit is reset by writing ‘0’ to this bit.

External Reset (RESETB) flag bit. The bit is reset by writing ‘0’ to this bit

or by Power-On Reset.

Watch Dog Reset flag bit. The bit is reset by writing ‘0’ to this bit or by

Power-On Reset.

On-Chip Debug Reset flag bit. The bit is reset by writing ‘0’ to this bit or by

Power-On Reset.

Low Voltage Reset flag bit. The bit is reset by writing ‘0’ to this bit or by

Power-On Reset.

NOTES) 1. When the Power-On Reset occurs, the PORF bit is only set to “1”, the other flag (WDTRF and

OCDRF) bits are all cleared to “0”.

2. When the Power-On Reset occurs, the EXTRF bit is unknown, At that time, the EXTRF bit can be set

to “1” when External Reset (RESETB) occurs.

3. When the Power-On Reset occurs, the LVRF bit is unknown, At that time, the LVRF bit can be set to

“1” when LVR Reset occurs.

4. When a reset except the POR occurs, the corresponding flag bit is only set to “1”, the other flag bits

are kept in the previous values.

Loading...

Loading...