MC96F6432

June 22, 2018 Ver. 2.9 223

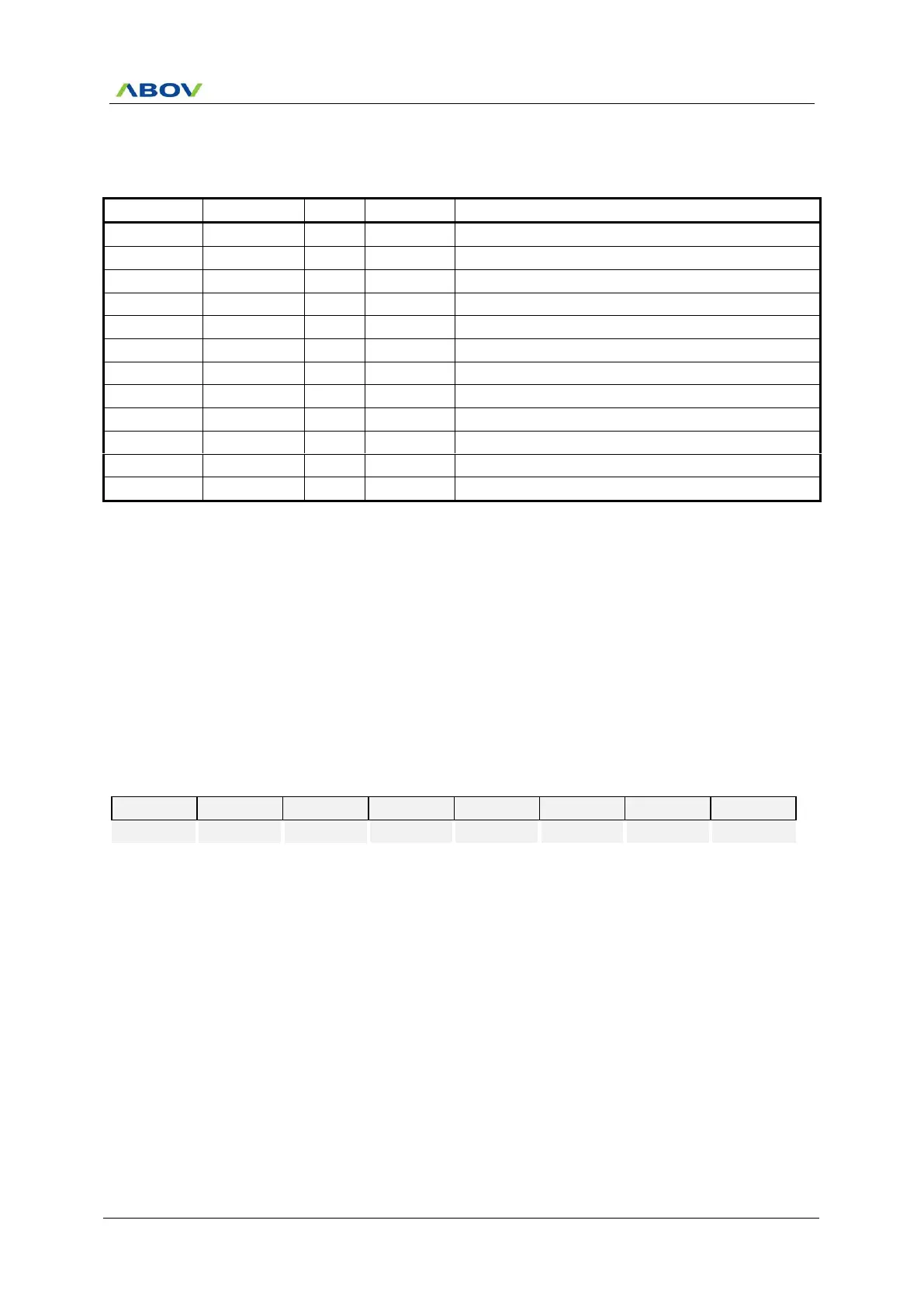

11.12.22 Register Map

Table 11-21 USI0 Register Map

USI0 Baud Rate Generation Register

USI0 SDA Hold Time Register

USI0 SCL High Period Register

USI0 SCL Low Period Register

USI0 Slave Address Register

11.12.23 USI0 Register Description

USI0 module consists of USI0 baud rate generation register (USI0BD), USI0 data register (USI0DR), USI0 SDA

hold time register (USI0SDHR), USI0 SCL high period register (USI0SCHR), USI0 SCL low period Register

(USI0SCLR), USI0 slave address register (USI0SAR), USI0 control register 1/2/3/4 (USI0CR1/2/3/4), USI0

status register 1/2 (USI0ST1/2).

11.12.24 Register Description for USI0

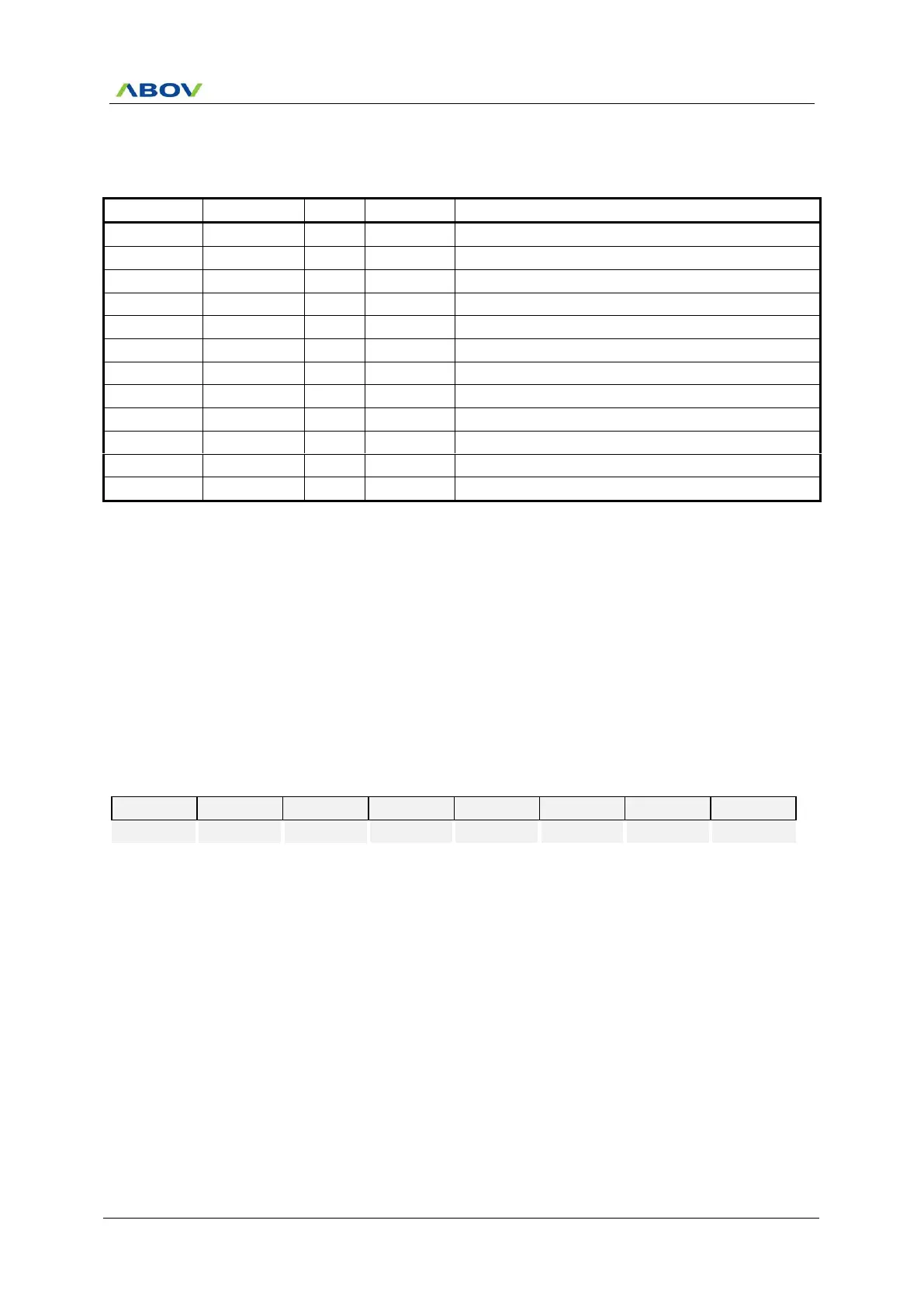

USI0BD (USI0 Baud- Rate Generation Register: For UART and SPI mode) : E3H

Initial value : FFH

The value in this register is used to generate internal baud rate in

asynchronous mode or to generate SCK0 clock in SPI mode. To

prevent malfunction, do not write ‘0’ in asynchronous mode and do

not write ‘0’ or ‘1’ in SPI mode.

NOTE) In common with USI0SAR register, USI0BD register is

used for slave address register when the USI0 I2C mode.

Loading...

Loading...