MC96F6432

June 22, 2018 Ver. 2.9 47

7.14 Data Retention Voltage in Stop Mode

Table 7-14 Data Retention Voltage in Stop Mode

(T

A

= -40°C ~ +85°C, VDD= 1.8V ~ 5.5V)

Data retention supply voltage

Data retention supply current

VDDR= 1.8V,

(T

A

= 25°C), Stop mode

Idle Mode

(Watchdog Timer Active)

V

DD

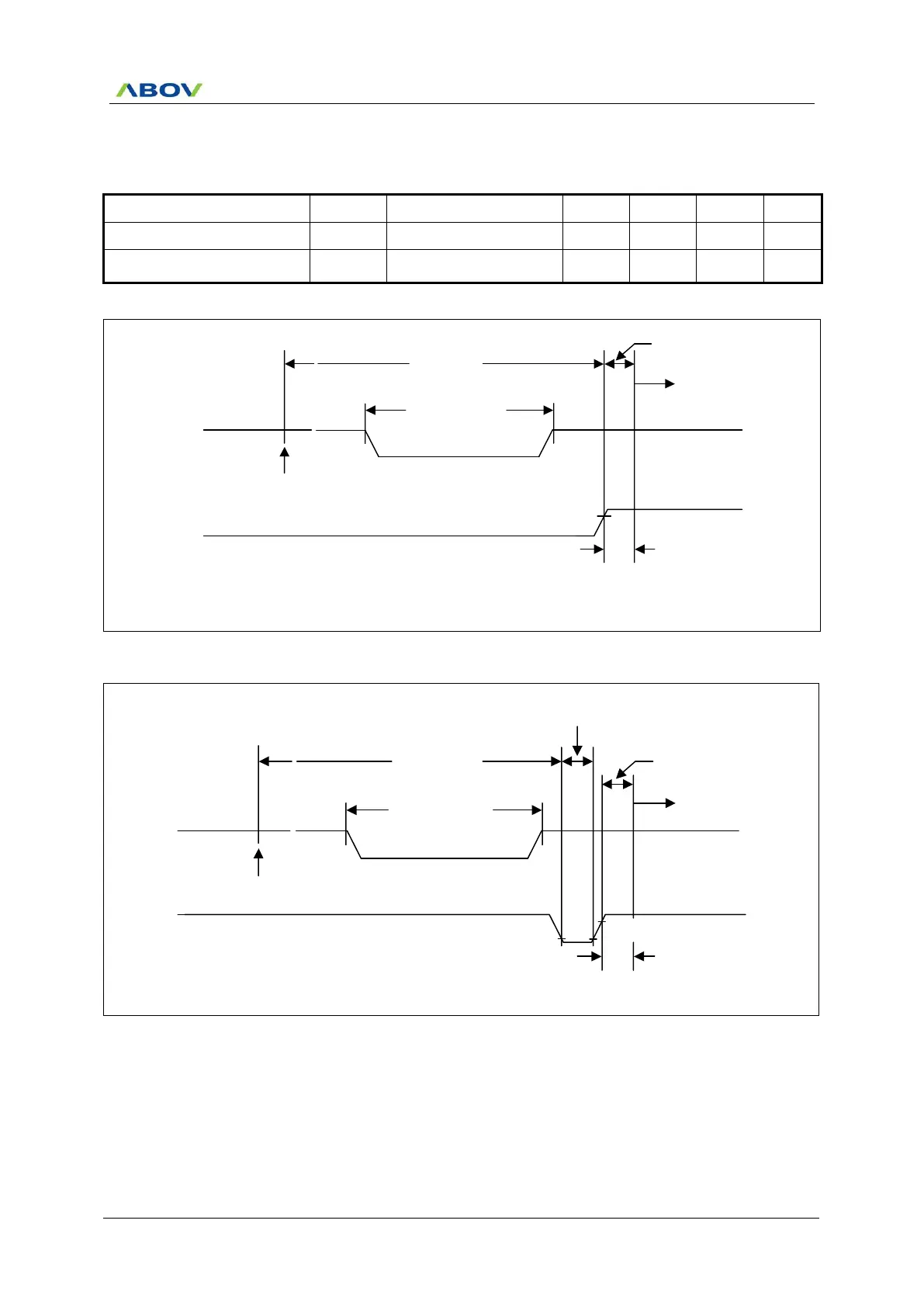

NOTE: tWAIT is the same as (the selected bit overflow of BIT) X 1/(BIT Clock)

INT Request

Execution of

STOP Instruction

~

~

Data Retention

~

~

Stop Mode

Normal

Operating Mode

0.8VDD

t

WAIT

V

DDDR

Figure 7.6 Stop Mode Release Timing when Initiated by an Interrupt

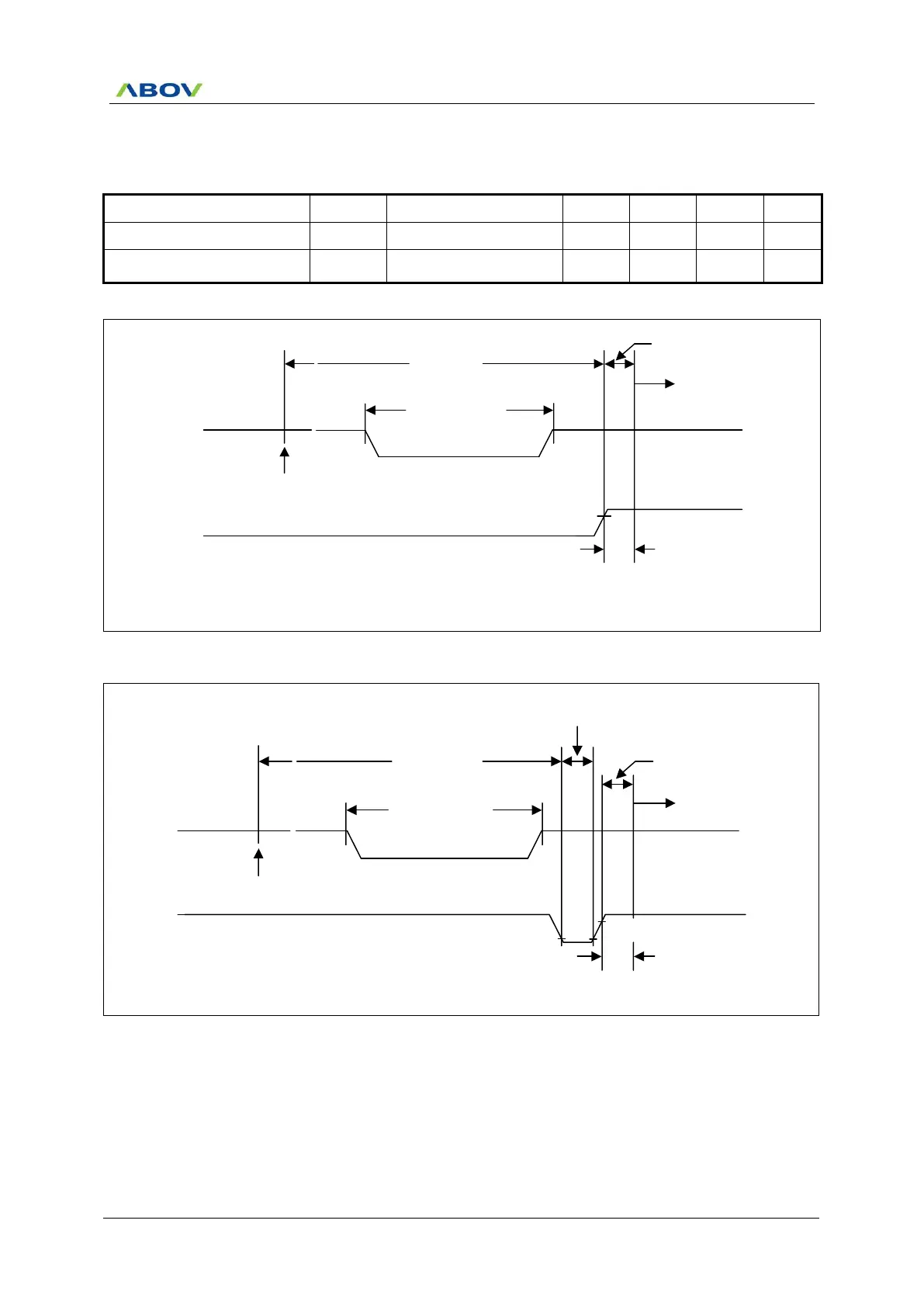

NOTE : tWAIT is the same as (4096 X 4 X 1/fx) (16.4ms @ 1MHz)

VDD

RESETB

Execution of

STOP Instruction

~

~

Data Retention

~

~

Stop Mode

Oscillation

Stabillization Time

Normal

Operating Mode

TWAIT

RESET

Occurs

0.2VDD

V

DDDR

0.8VDD

Figure 7.7 Stop Mode Release Timing when Initiated by RESETB

Loading...

Loading...