MC96F6432

118 June 22, 2018 Ver. 2.9

11.3.6 Register Description for Watch Dog Timer

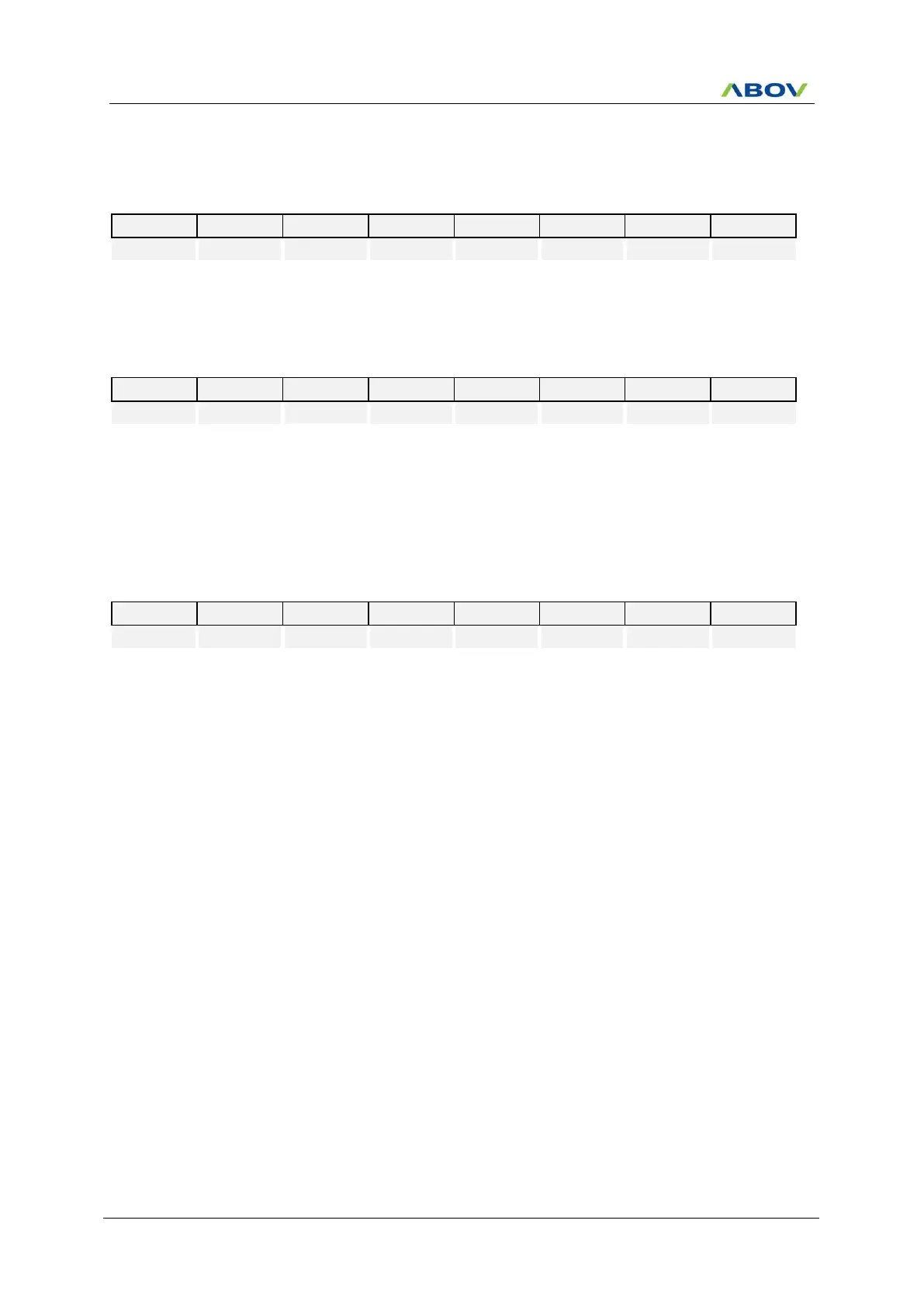

WDTCNT (Watch Dog Timer Counter Register: Read Case) : 8EH

Initial value : 00H

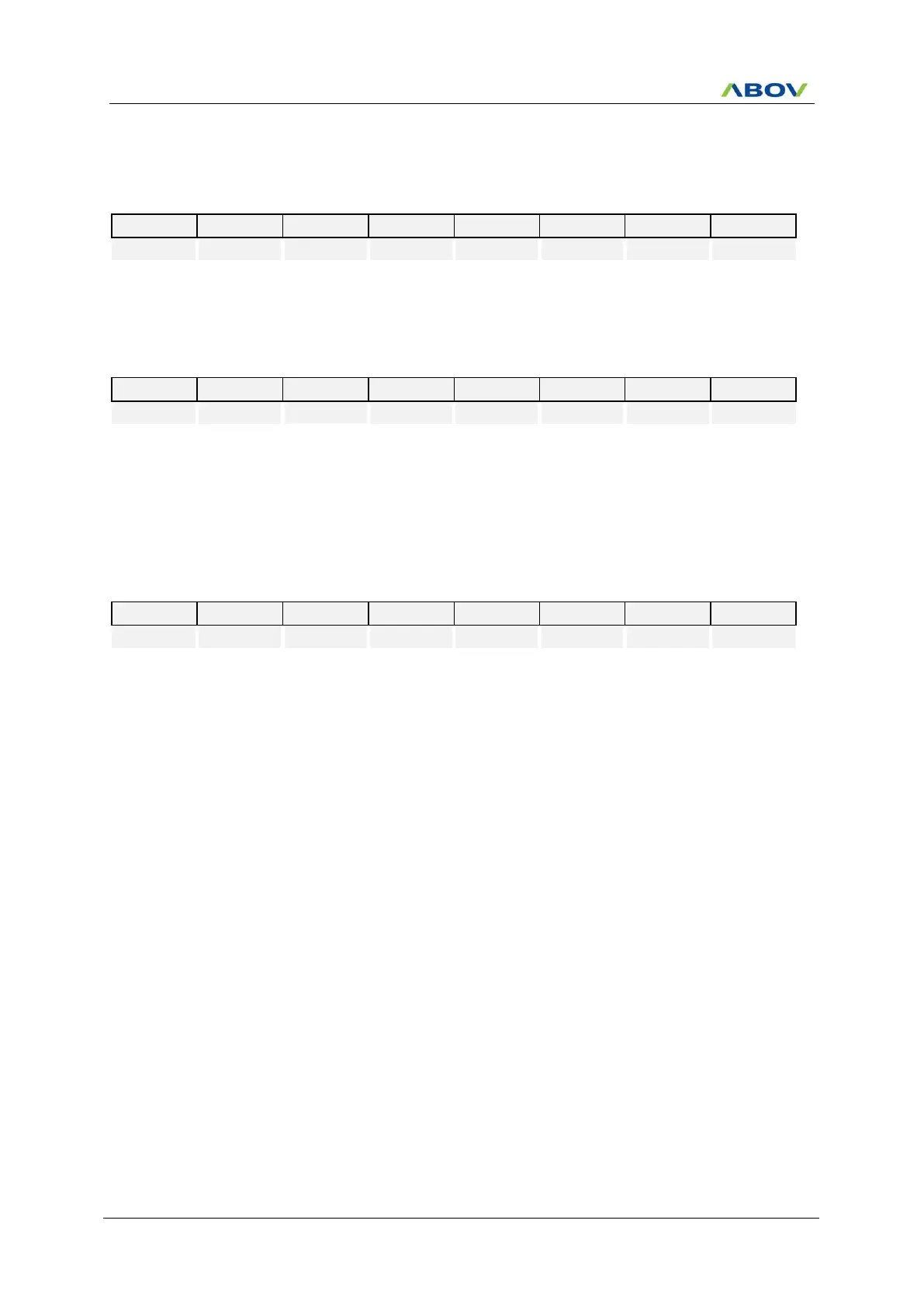

WDTDR (Watch Dog Timer Data Register: Write Case) : 8EH

Initial value : FFH

Set a period

WDT Interrupt Interval=(BIT Interrupt Interval) x(WDTDR Value+1)

NOTE) Do not write “0” in the WDTDR register.

WDTCR (Watch Dog Timer Control Register) : 8DH

Initial value : 00H

Control WDT RESET Operation

Clear WDT Counter (auto clear after 1 Cycle)

Control WDT Clock Selection Bit

BIT overflow for WDT clock (WDTRC disable)

WDTRC for WDT clock (WDTRC enable)

When WDT Interrupt occurs, this bit becomes ‘1’. For clearing bit, write

‘0’ to this bit or auto clear by INT_ACK signal. Writing “1” has no effect.

WDT Interrupt no generation

Loading...

Loading...