MC96F6432

130 June 22, 2018 Ver. 2.9

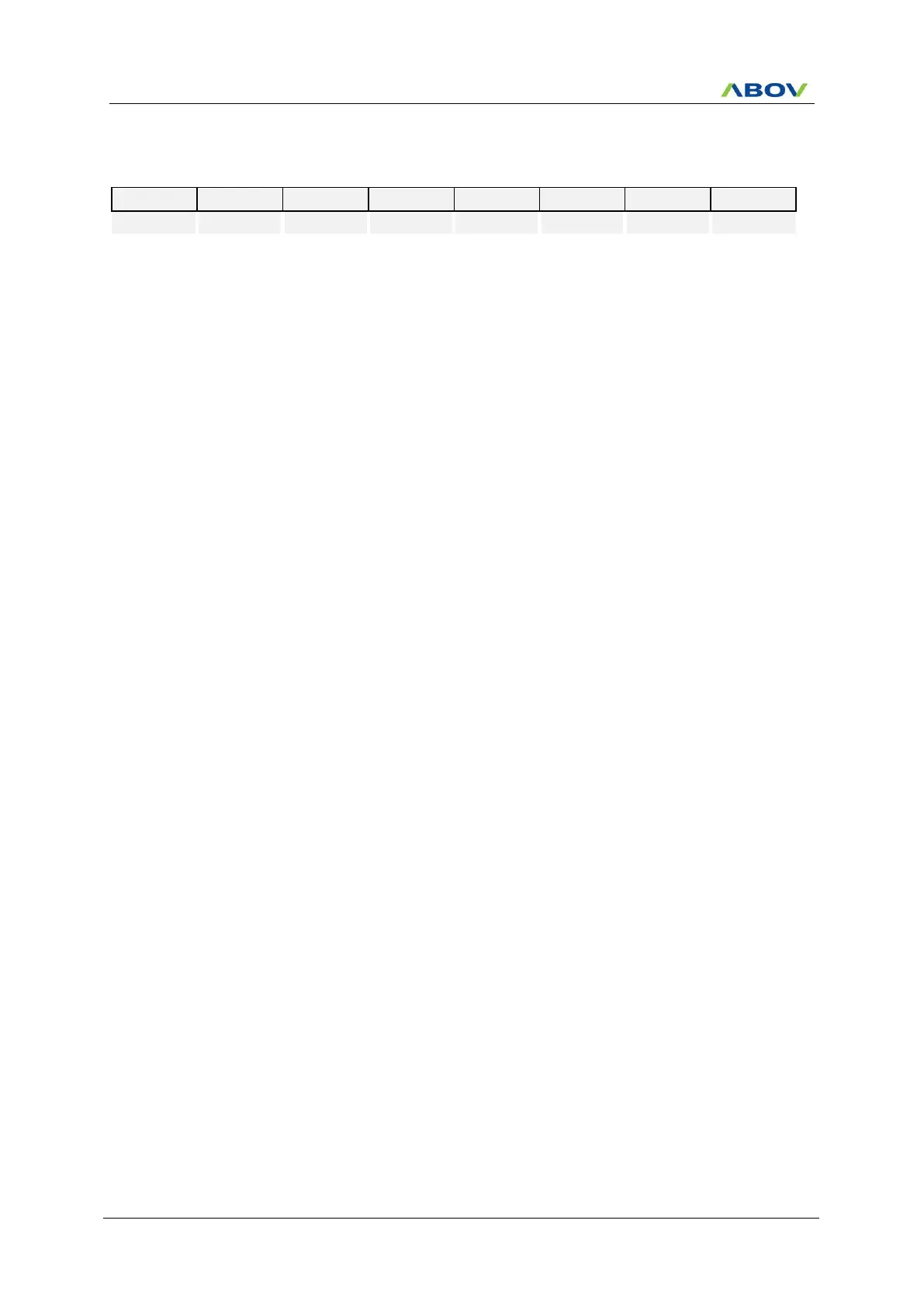

T0CR (Timer 0 Control Register) : B2H

Initial value : 00H

Control Timer 0 Operation Mode

Select Timer 0 clock source. fx is a system clock frequency

Clear the Timer 0 counter (When write, automatically cleared

“0” after being cleared counter)

NOTES) 1. Match Interrupt is generated in Capture mode.

2. Refer to the external interrupt flag 1 register (EIFLAG1) for the T0 interrupt flags.

Loading...

Loading...