MC96F6432

180 June 22, 2018 Ver. 2.9

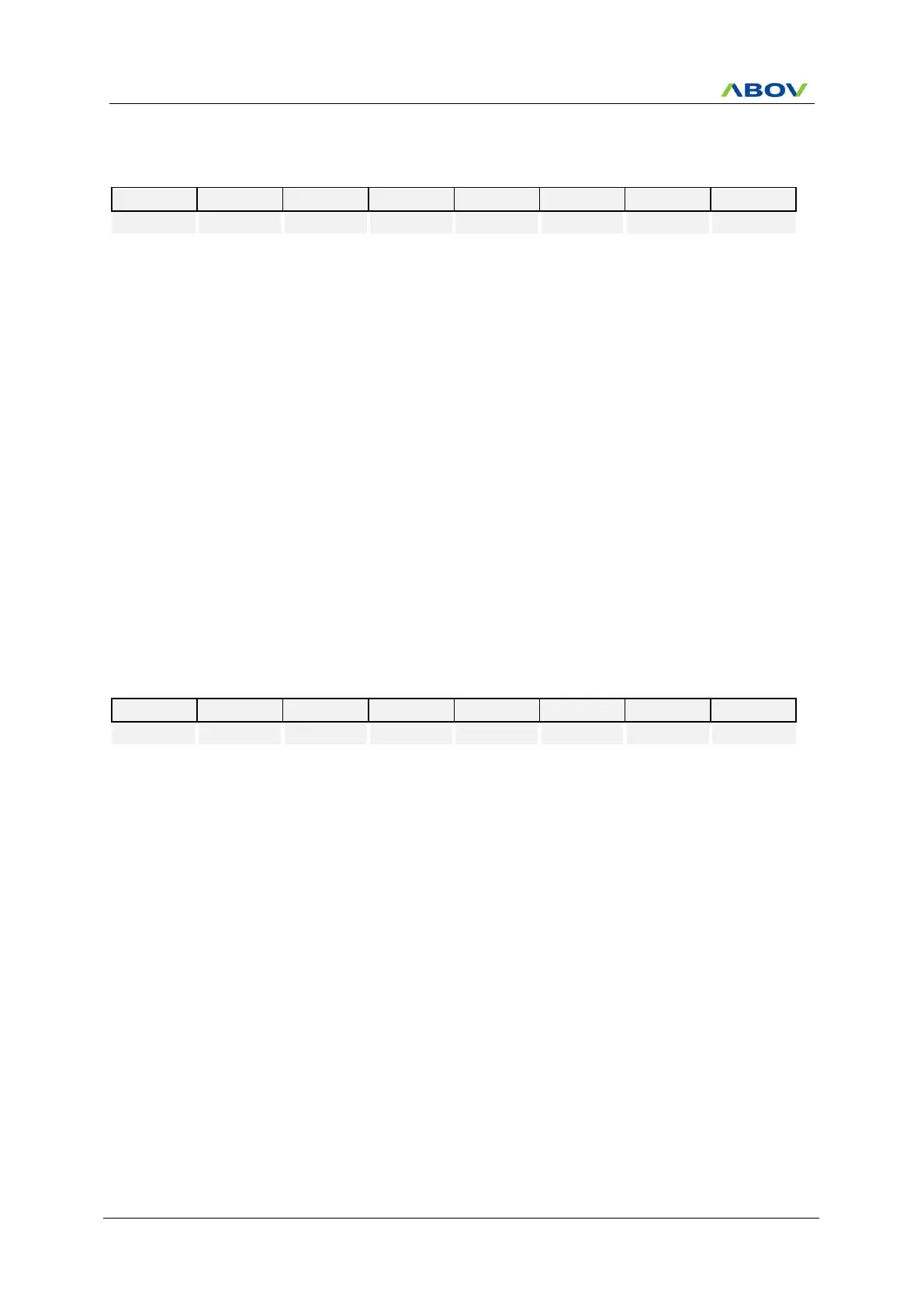

T4ISR (Timer 4 Interrupt Status Register) : 1006H (ESFR)

Initial value : 00H

Timer 4 Overflow Interrupt Status, Write ‘0’ to this bit for clear

Timer 4 Bottom Interrupt Status, Write ‘0’ to this bit for clear

(In the Back-to-Back mode)

Timer 4 Compare Match or PWM A-ch Match Interrupt Status, Write ‘0’

to this bit for clear

Compare match or PWM A-ch match no occurrence

Compare match or PWM A-ch match occurrence

Timer 4 PWM B-ch Match Interrupt Status, Write ‘0’ to this bit for clear

PWM B-ch match no occurrence

PWM B-ch match occurrence

Timer 4 PWM C-ch Match Interrupt Status, Write ‘0’ to this bit for clear

PWM C-ch match no occurrence

PWM C-ch match occurrence

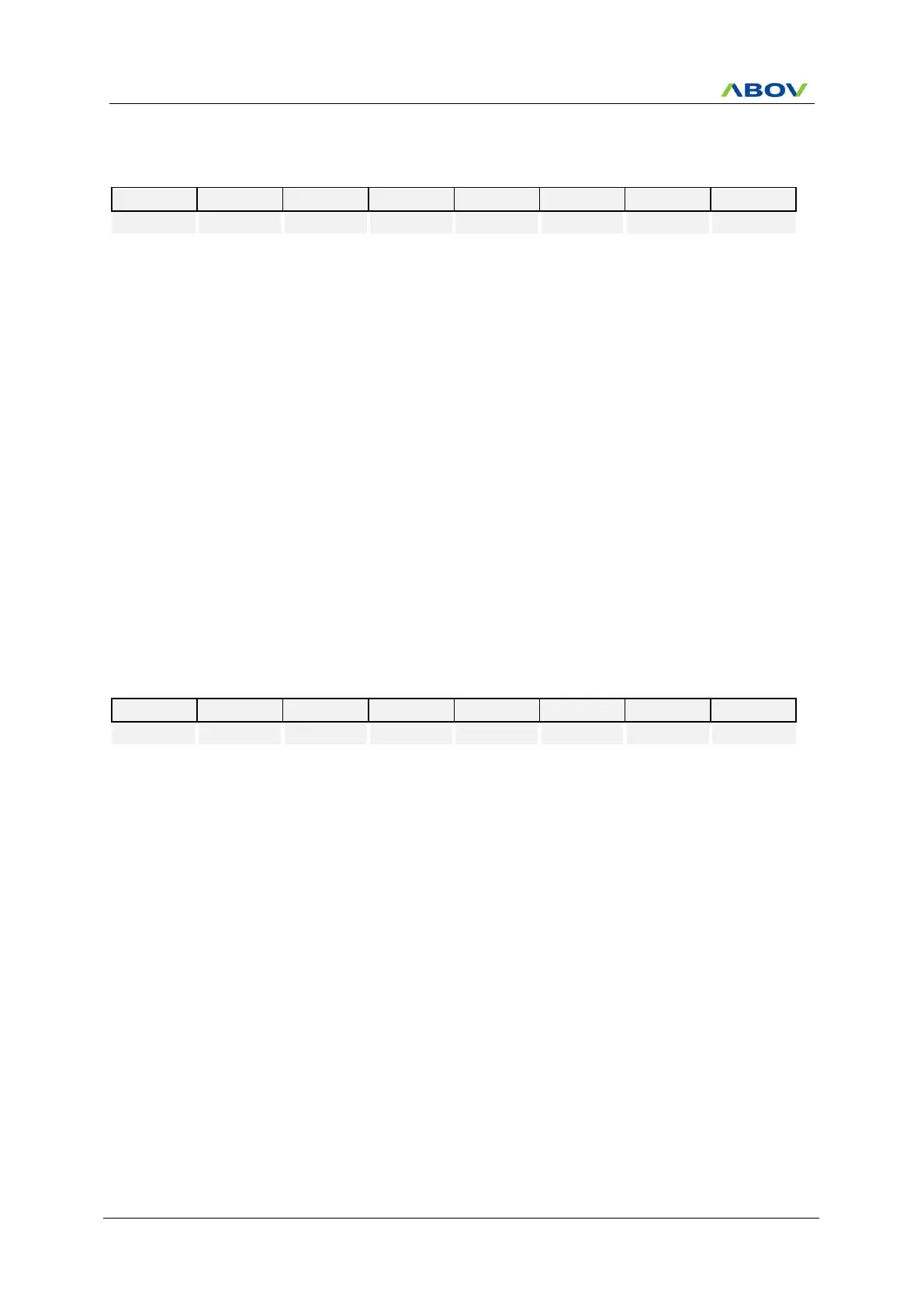

T4MSK (Timer 4 Interrupt Mask Register) : 1007H (ESFR)

Initial value : 00H

Control Timer 4 Overflow Interrupt

Disable overflow interrupt

Enable overflow interrupt

Control Timer 4 Bottom Interrupt

Control Timer 4 Compare Match or PWM A-ch Match Interrupt

Disable compare match or PWM A-ch match interrupt

Enable compare match or PWM A-ch match interrupt

Control Timer 4 PWM B-ch Match Interrupt

Disable PWM B-ch match interrupt

Enable PWM B-ch match interrupt

Control Timer 4 PWM C-ch Match Interrupt

Disable PWM C-ch match interrupt

Enable PWM C-ch match interrupt

Loading...

Loading...