MC96F6432

230 June 22, 2018 Ver. 2.9

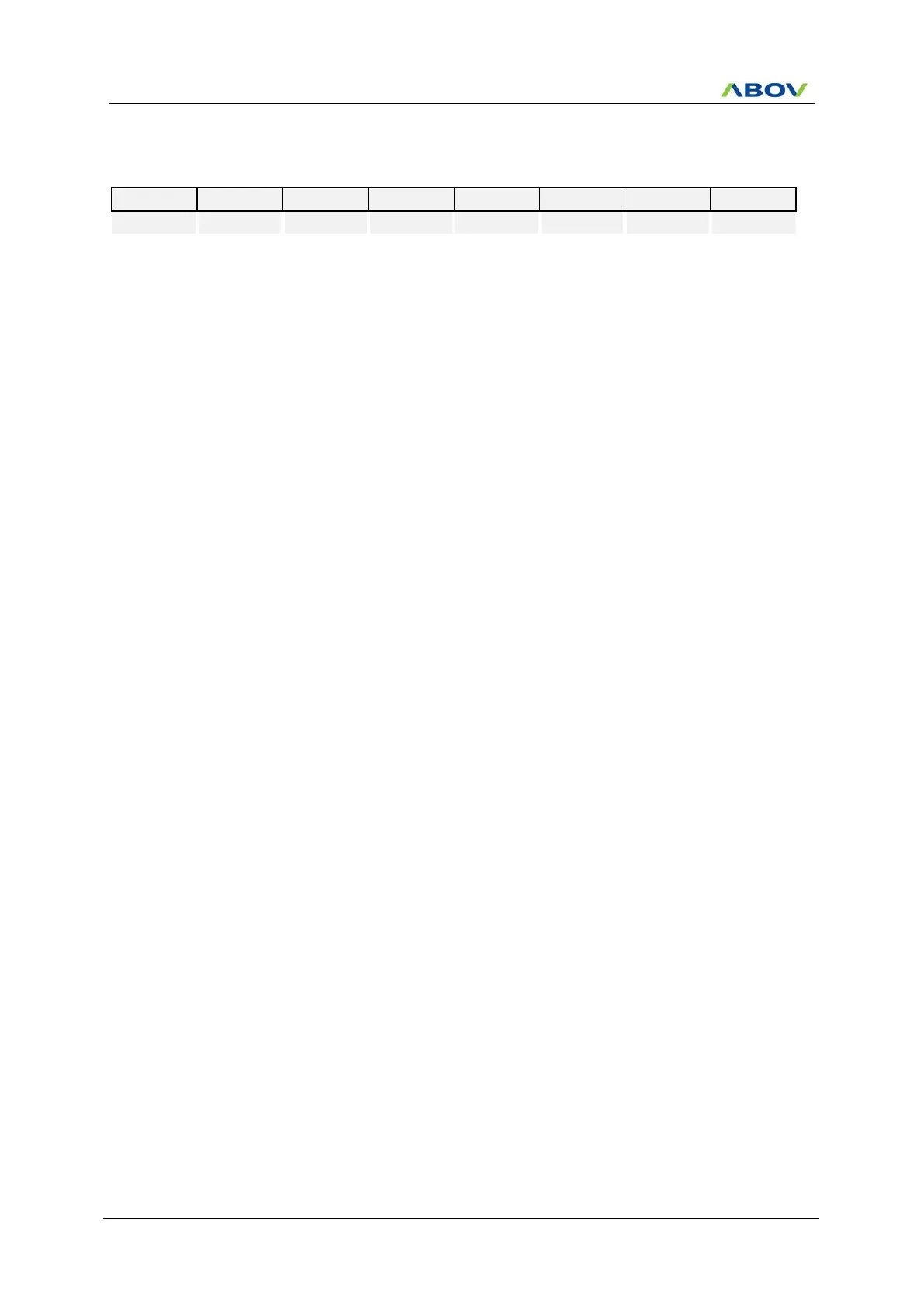

USI0ST1 (USI0 Status Register 1: For UART and SPI mode) : E1H

Initial value : 80H

The DRE0 flag indicates if the transmit buffer (USI0DR) is ready to

receive new data. If DRE0 is ‘1’, the buffer is empty and ready to be

written. This flag can generate a DRE0 interrupt.

Transmit buffer is not empty.

Transmit buffer is empty.

This flag is set when the entire frame in the transmit shift register has

been shifted out and there is no new data currently present in the

transmit buffer. This flag is automatically cleared when the interrupt

service routine of a TXC0 interrupt is executed. This flag can generate a

TXC0 interrupt. This bit is automatically cleared.

Transmit buffer is empty and the data in transmit shift register

are shifted out completely.

This flag is set when there are unread data in the receive buffer and

cleared when all the data in the receive buffer are read. The RXC0 flag

can be used to generate a RXC0 interrupt.

There is no data unread in the receive buffer

There are more than 1 data in the receive buffer

This flag is set when the RXD0 pin is detected low while the CPU is in

STOP mode. This flag can be used to generate a WAKE0 interrupt. This

bit is set only when in asynchronous mode of operation. This bit should

be cleared by program software. (only UART mode)

No WAKE interrupt is generated.

WAKE interrupt is generated

This is an internal reset and only has effect on USI0. Writing ‘1’ to this bit

initializes the internal logic of USI0 and this bit is automatically cleared to

‘0’.

This bit is set if a Data OverRun occurs. While this bit is set, the

incoming data frame is ignored. This flag is valid until the receive buffer

is read.

This bit is set if the first stop bit of next character in the receive buffer is

detected as ‘0’. This bit is valid until the receive buffer is read. (only

UART mode)

This bit is set if the next character in the receive buffer has a Parity Error

to be received while Parity Checking is enabled. This bit is valid until the

receive buffer is read. (only UART mode)

Loading...

Loading...