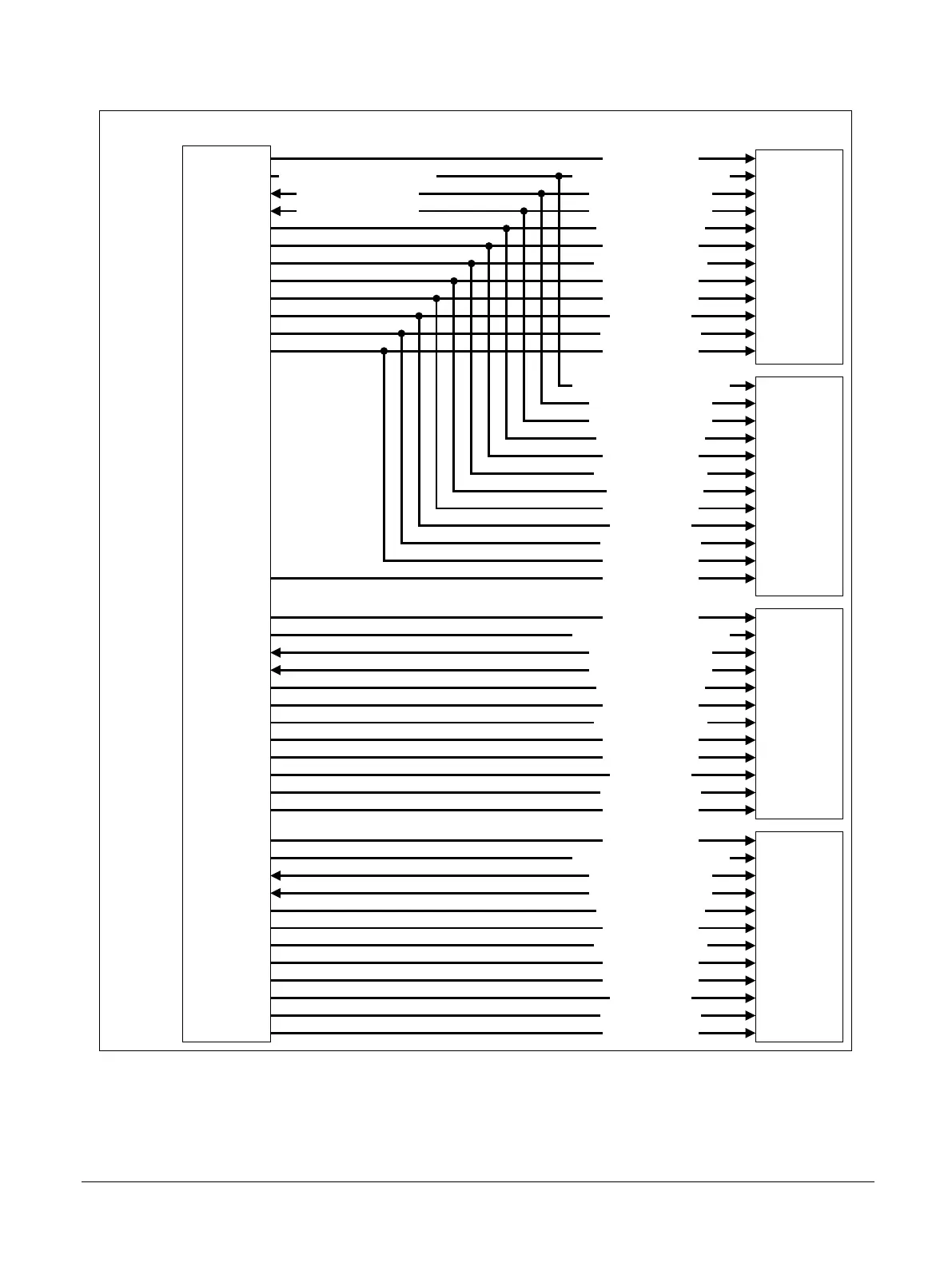

MPS2/MPS2+ FPGA Prototyping Board

FPGA

ZBT

SSRAM

2MB

ZBT

SSRAM

2MB

ZBT

SSRAM

2MB

SSRAM1_nCE1

SSRAM1_MODE

SSRAM1_ZZ

SSRAM1_nCEN

SSRAM1_nOE

SSRAM1_ADVnLD

SSRAM1_nWE

SSRAM1_A[18:0]

SSRAM1_DQP[7:4]

SSRAM1_DQ[63:0]

SSRAM1_ADV_nBW[7:0] SSRAM1_ADV_nBW[7:4]

SSRAM1_ADV_nBW[3:0]

SSRAM1_CLK1

SSRAM1_DQ[63:32]

SSRAM1_DQ[31:0]

SSRAM1_DQP[7:0]

SSRAM1_DQP[3:0]

SSRAM1_A[18:0]

SSRAM1_nWE

SSRAM1_ADVnLD

SSRAM1_nOE

SSRAM1_nCEN

SSRAM1_ZZ

SSRAM1_MODE

SSRAM1_nCE1

SSRAM1_CLK0

SSRAM2_CLK

SSRAM2_ADV_nBW[3:0]

SSRAM2_DQ[31:0]

SSRAM2_DQP[3:0]

SSRAM2_A[18:0]

SSRAM2_nWE

SSRAM2_ADVnLD

SSRAM2_nOE

SSRAM2_nCEN

SSRAM2_ZZ

SSRAM2_MODE

SSRAM2_nCE1

ZBT

SSRAM

2MB

SSRAM3_CLK

SSRAM3_ADV_nBW[3:0]

SSRAM3_DQ[31:0]

SSRAM3_DQP[3:0]

SSRAM3_A[18:0]

SSRAM3_nWE

SSRAM3_ADVnLD

SSRAM3_nOE

SSRAM3_nCEN

SSRAM3_ZZ

SSRAM3_MODE

SSRAM3_nCE1

Figure 2-12 ZBT SSRAM external user memory interface

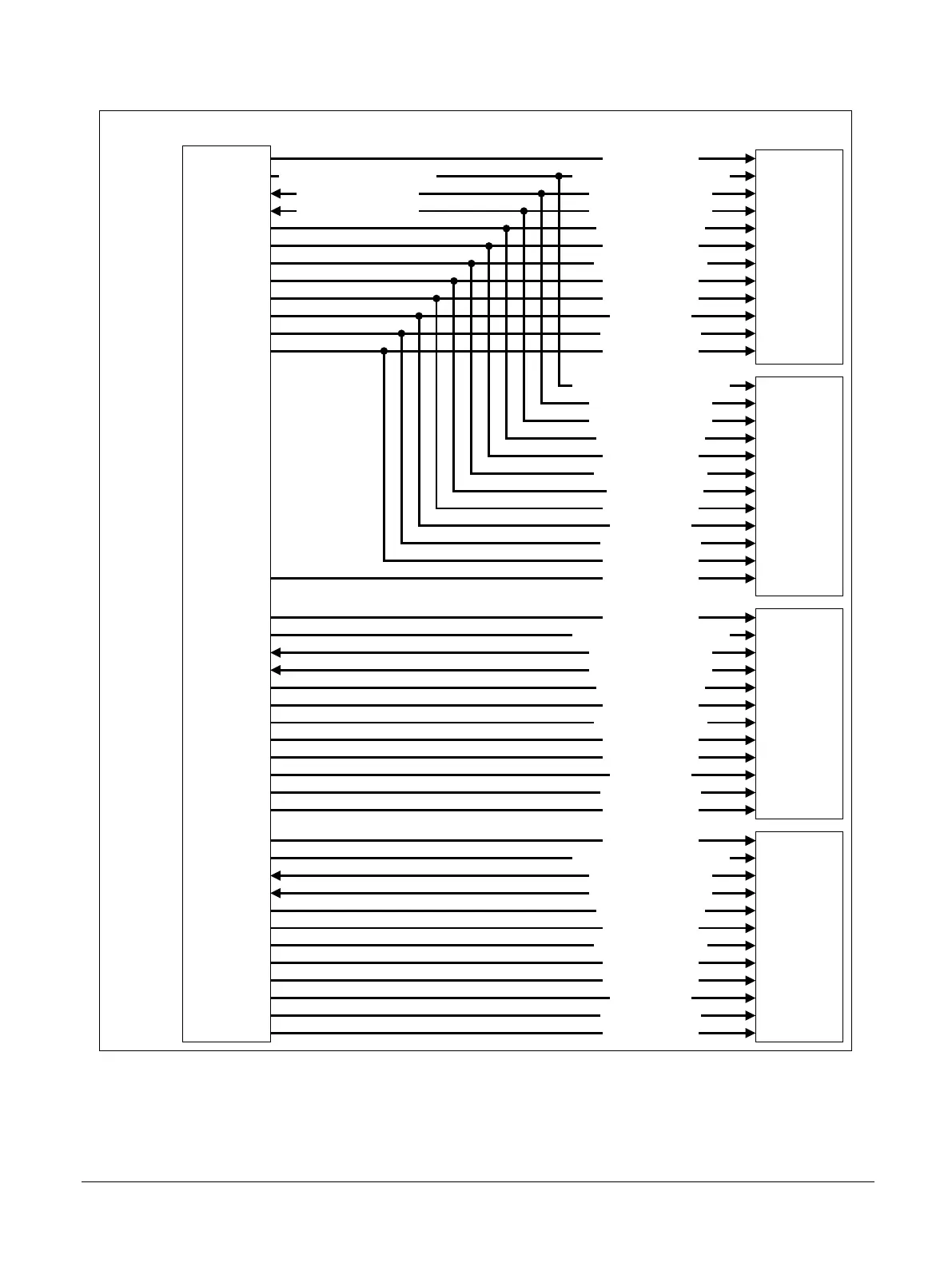

The following diagram shows the external PSRAM user memory interface.

2 Hardware Description

2.12 External user memory

100112_0200_09_en Copyright © 2013–2016, 2018–2020 Arm Limited or its affiliates. All

rights reserved.

2-37

Non-Confidential

Loading...

Loading...