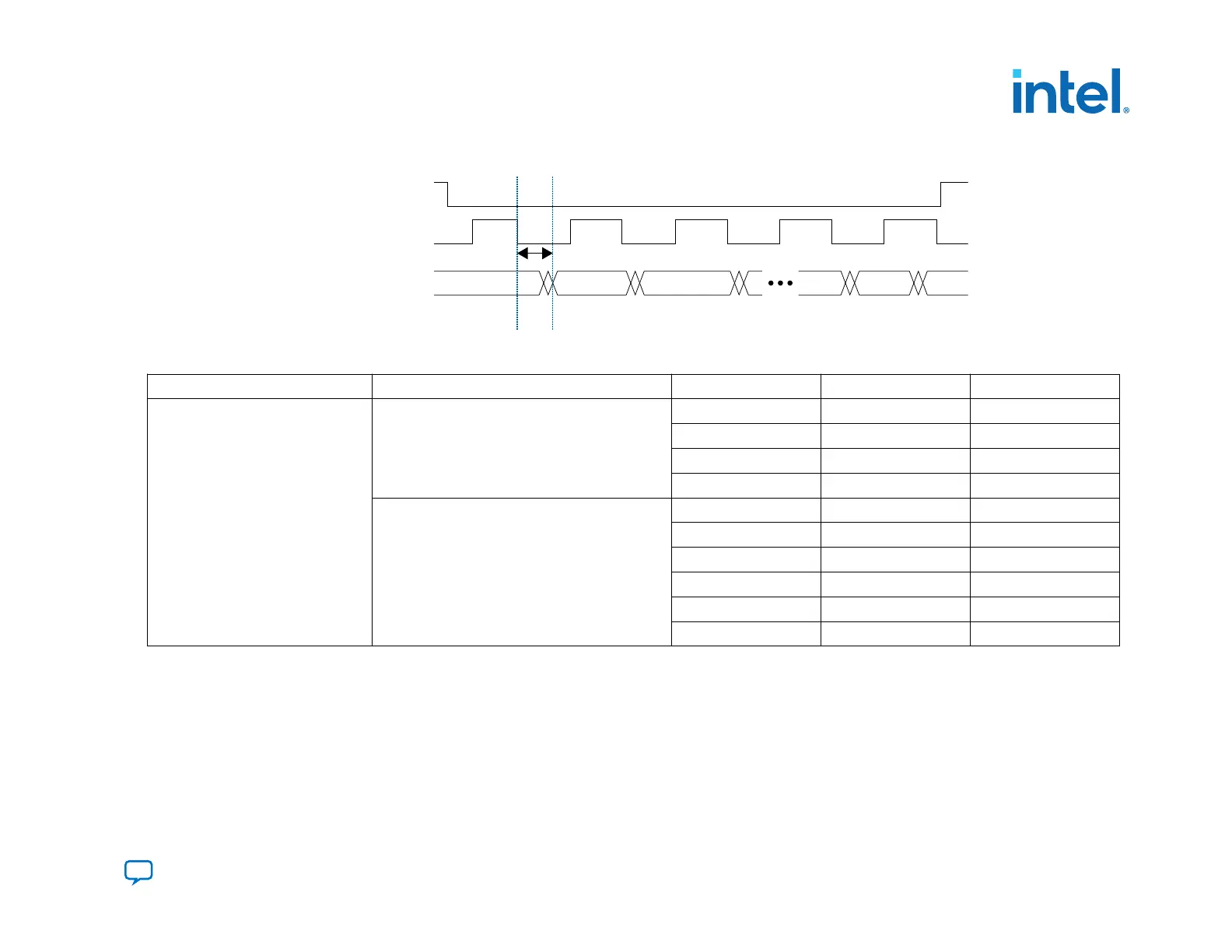

Figure 41. AS Configuration Serial Input Timing Diagram

nCSO

AS_CLK

AS_DATA IN0 IN1 INn

T

ext_delay

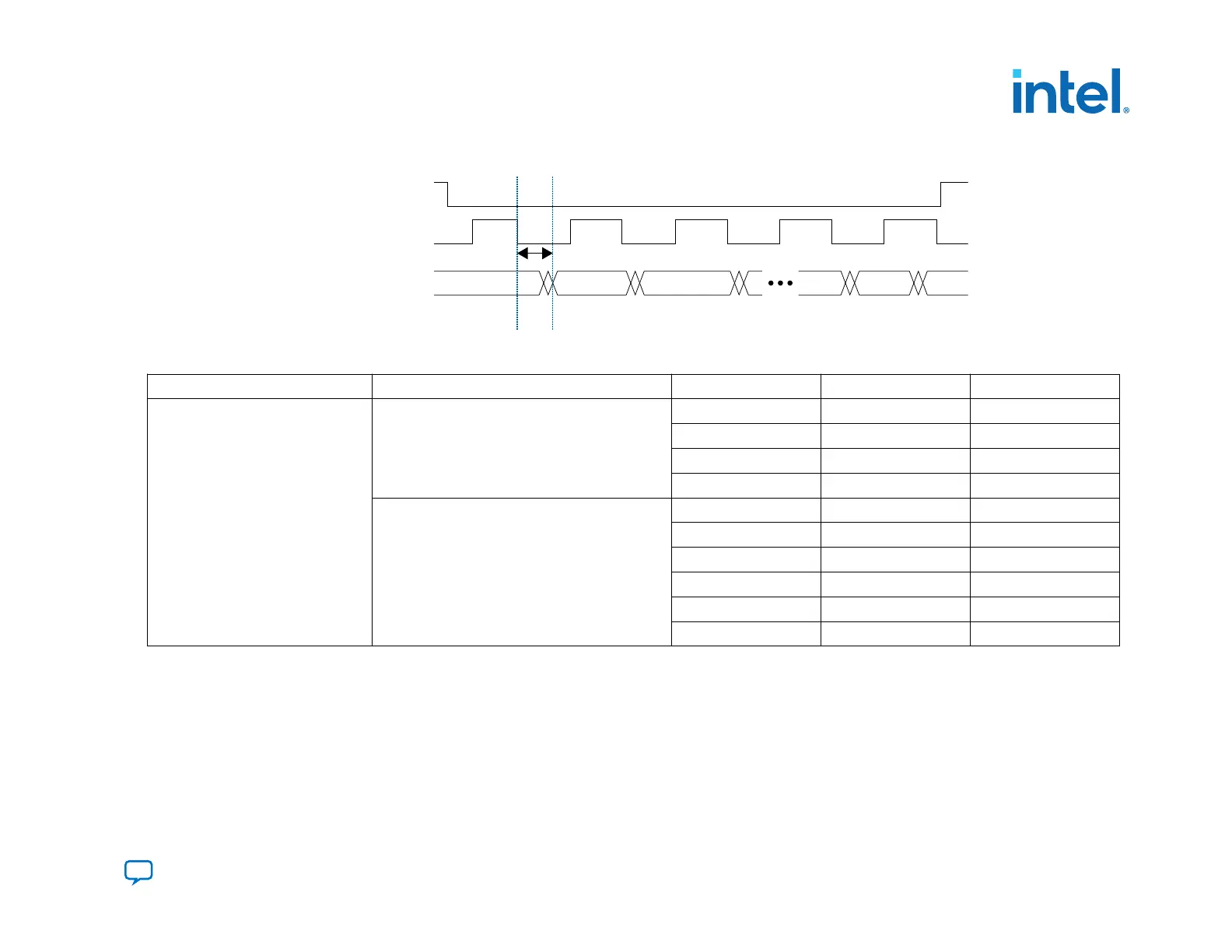

Table 34.

T

ext_delay

as a Function of AS_CLK Frequency

Symbol Configuration Clock Source Frequency Min (ns) Max (ns)

T

ext_delay

Internal Oscillator 115 MHz 0 20

77 MHz 0 20

58 MHz 0 20

25 MHz 0 24

OSC_CLK_1 166 MHz 0 13.5

125 Mhz 0 18

100 MHz 0 24

71.5 MHz 0 35

50 MHz 0 24

25 MHz 0 24

Note: For more information about the timing parameters, refer to the Intel Agilex Device Datasheet.

3.2.5. Maximum Allowable External AS_DATA Pin Skew Delay Guidelines

You must minimize the skew on the AS data pins.

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

109

Loading...

Loading...