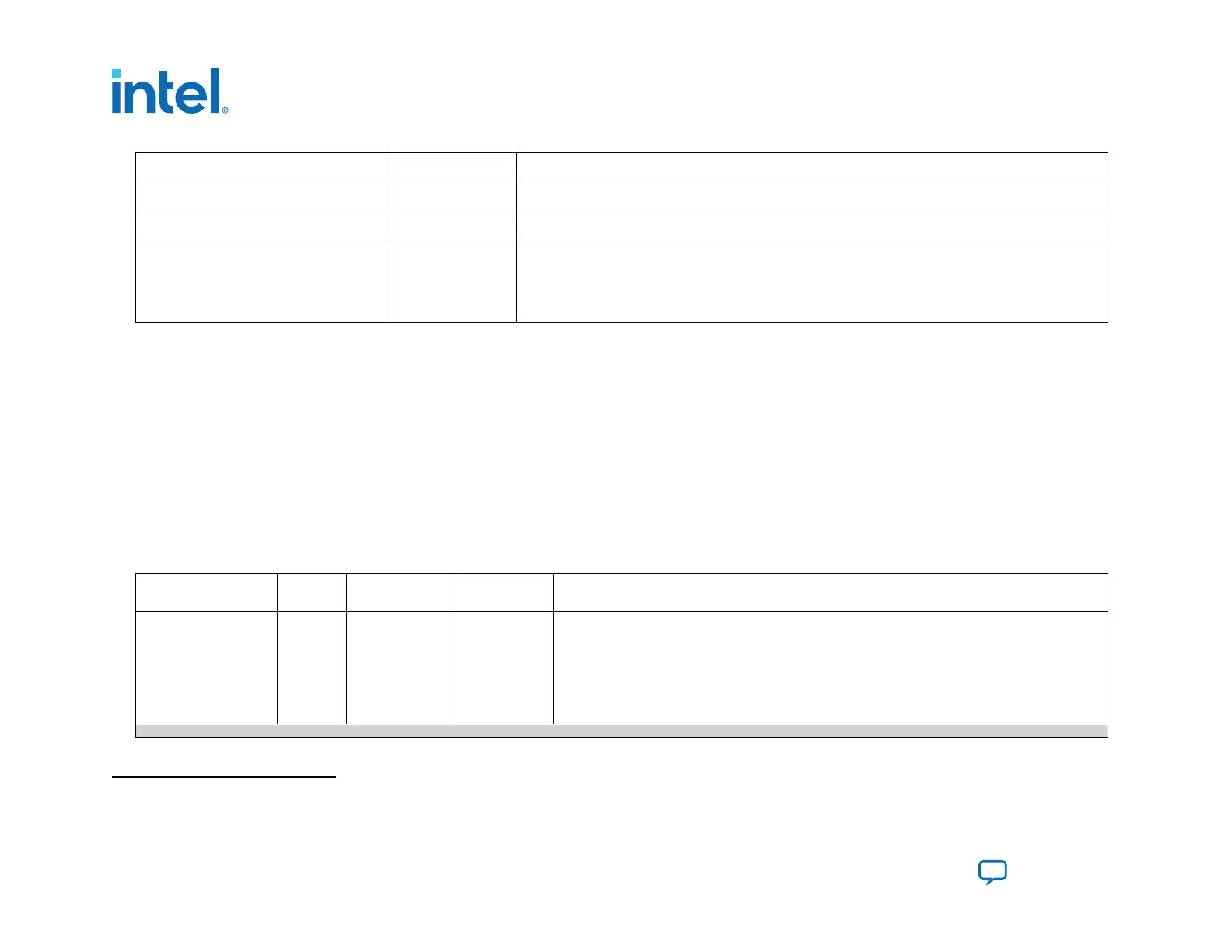

Header Bit Description

LENGTH

[22:12] Number of words of arguments following the header. The IP responds with an error if a wrong number of

words of arguments is entered for a given command.

Reserved [11] Reserved. Must be set to 0.

Command Code/Error Code

[10:0]

Command Code specifies the command. The Error Code indicates whether the command succeeded or

failed.

In the command header, these bits represent command code. In the response header, these bits

represent error code. If the command succeeds, the Error Code is 0. If the command fails, refer to the

error codes defined in the Error Code Responses.

5.3.1. Operation Commands

Resetting Quad SPI Flash

Important:

For Intel Agilex devices, you must connect the serial flash or quad SPI flash reset pin to the AS_nRST pin. The SDM must fully

control the QSPI reset. Do not connect the quad SPI reset pin to any external host.

RSU SDM Command Use Case

Important:

All RSU-related SDM commands (RSU_IMAGE_UPDATE, RSU_GET_SPT, RSU_STATUS, and RSU_NOTIFY) are only valid when

the FPGA loads the RSU image from QSPI flash using AS x4 configuration mode.

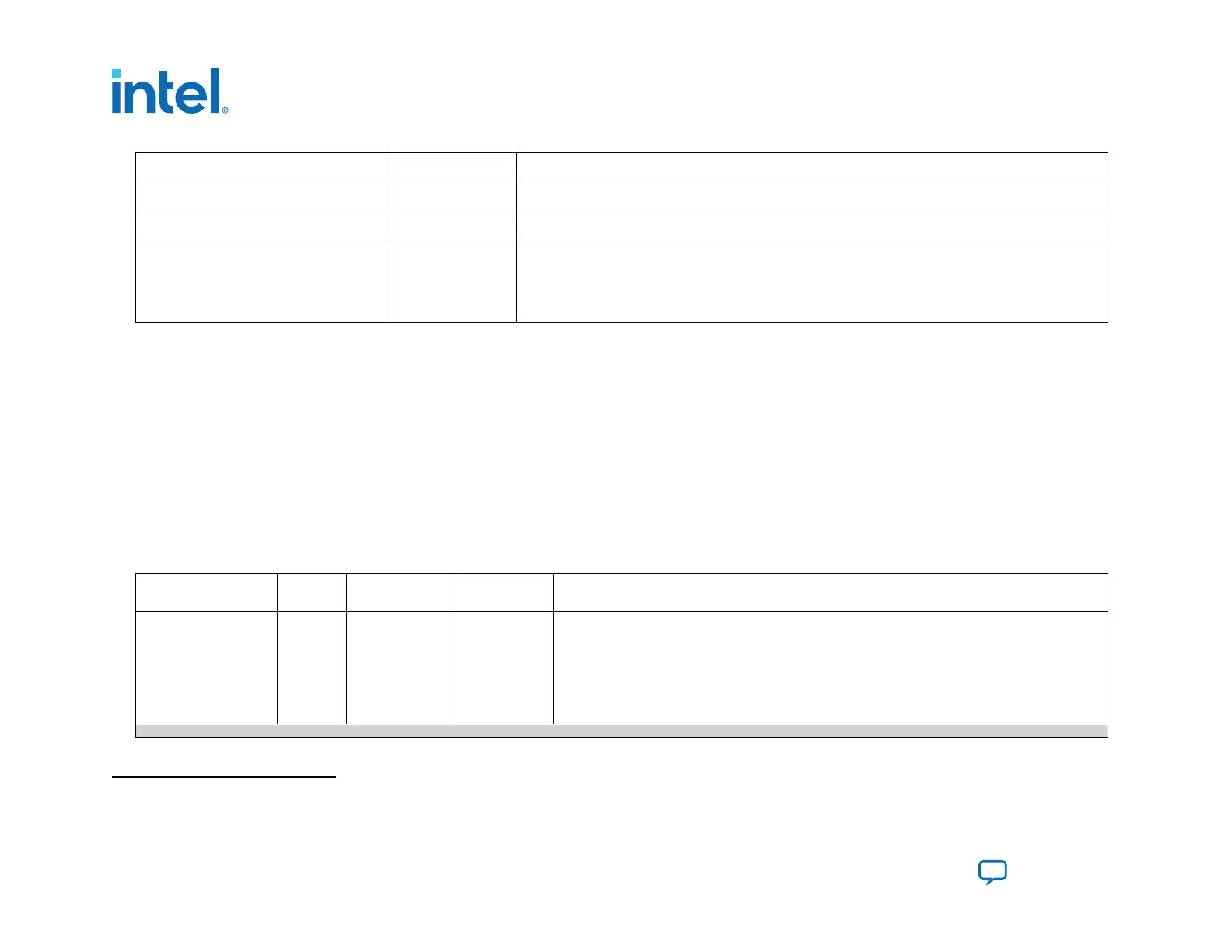

Table 41. Command List and Description

Command Code

(Hex)

Command

Length

(14)

Response

Length

(14)

Description

RSU_IMAGE_UPDATE

5C 2 0 Triggers reconfiguration from the data source that can be either the factory or an application

image.

This command takes an optional 64-bit argument that specifies the reconfiguration data address

in the flash. When sending the argument to the IP, you first send bits [31:0] followed by bits

[63:32]. If you do not provide this argument its value is assumed to be 0.

• Bit [31:0]: The start address of an application image.

• Bit [63:32]: Reserved (write as 0).

continued...

(14)

This number does not include the command or response header.

5. Remote System Update (RSU)

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

158

Loading...

Loading...