Command Code

(Hex)

Command

Length

(14)

Response

Length

(14)

Description

Once the device processes this command, it returns the response header to response FIFO before

it proceeds to reconfigure the device. Ensure the host PC or host controller stops servicing other

interrupts and focuses on reading the response header data to indicate the command completed

successfully. Otherwise, the host PC or host controller may not be able to receive the response

once the reconfiguration process started.

Once the device proceeds with reconfiguration, the link between the external host and FPGA is

lost. If you use PCIe in your design, you need to re-enumerate the PCIe link.

Important: When resetting quad SPI, you must follow instructions specified in Resetting Quad

SPI Flash on page 158.

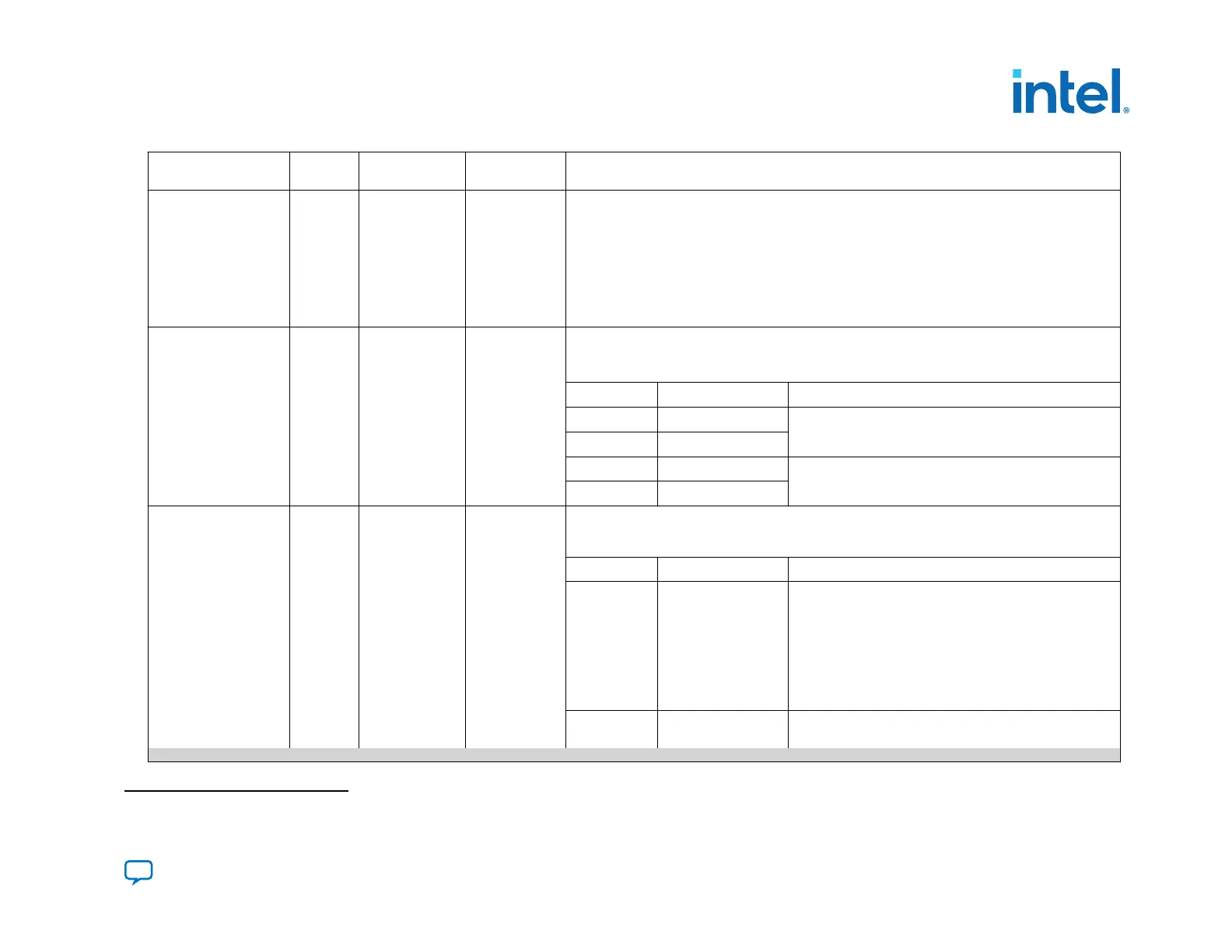

RSU_GET_SPT

5A 0 4

RSU_GET_SPT retrieves the quad SPI flash location for the two sub-partition tables that the RSU

uses: SPT0 and SPT1.

The 4-word response contains the following information:

Word Name Description

0 SPT0[63:32]

SPT0 address in quad SPI flash.

1 SPT0[31:0]

2 SPT1[63:32]

SPT1 address in quad SPI flash.

3 SPT1[31:0]

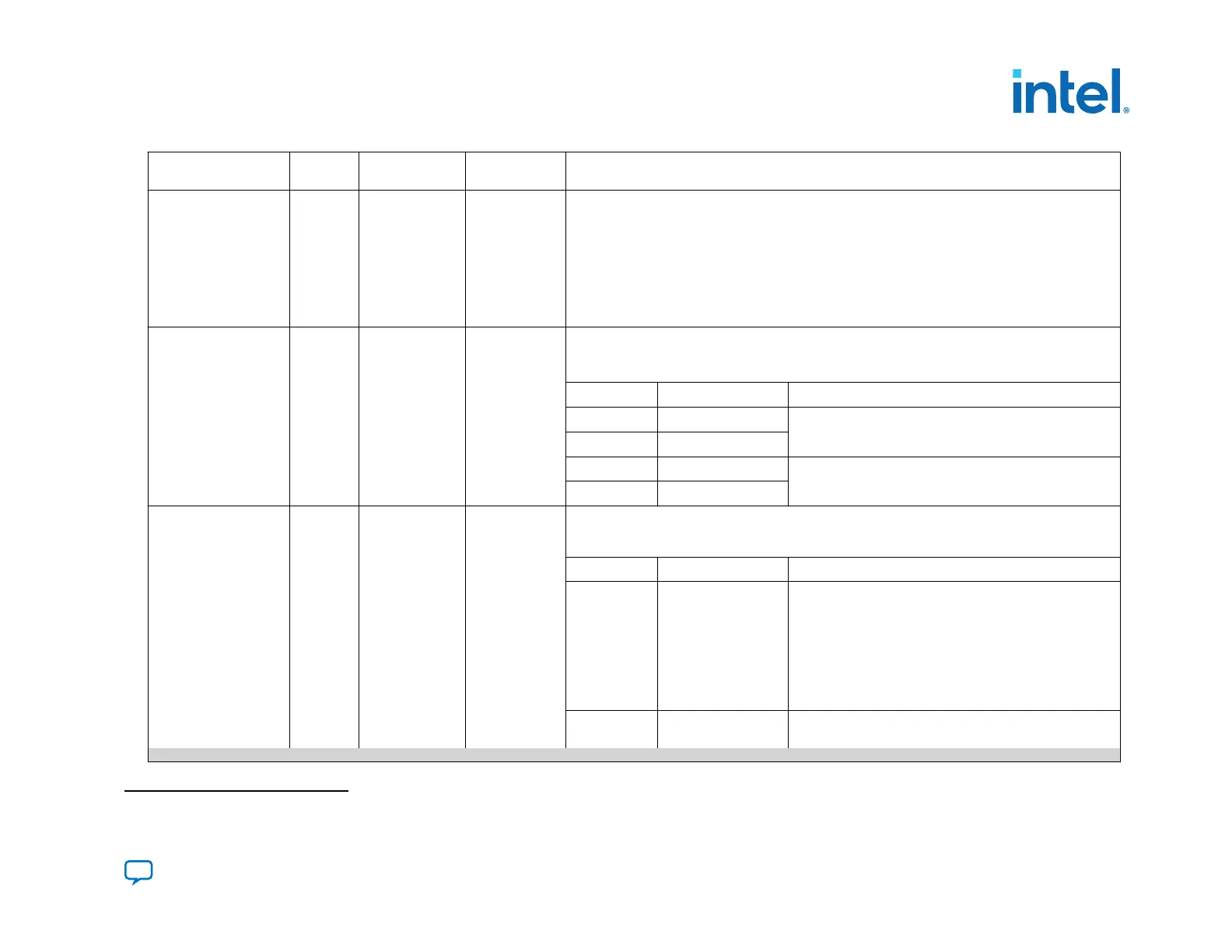

CONFIG_STATUS

4 0 6 Reports the status of the last reconfiguration. You can use this command to check the

configuration status during and after configuration. The response contains the following

information:

Word Summary Description

0 State Describes the most recent configuration related error.

Returns 0 when there are no configuration errors.

The error field has 2 fields:

• Upper 16 bits: Major error code.

• Lower 16 bits: Minor error code.

Refer to Appendix: CONFIG_STATUS and RSU_STATUS

Error Code Descriptions in the Mailbox Client Intel FPGA

IP User Guide for more information.

1 Quartus Version Available in Intel Quartus Prime software versions

between 19.4 and 21.2, the field displays:

continued...

(14)

This number does not include the command or response header.

5. Remote System Update (RSU)

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

159

Loading...

Loading...