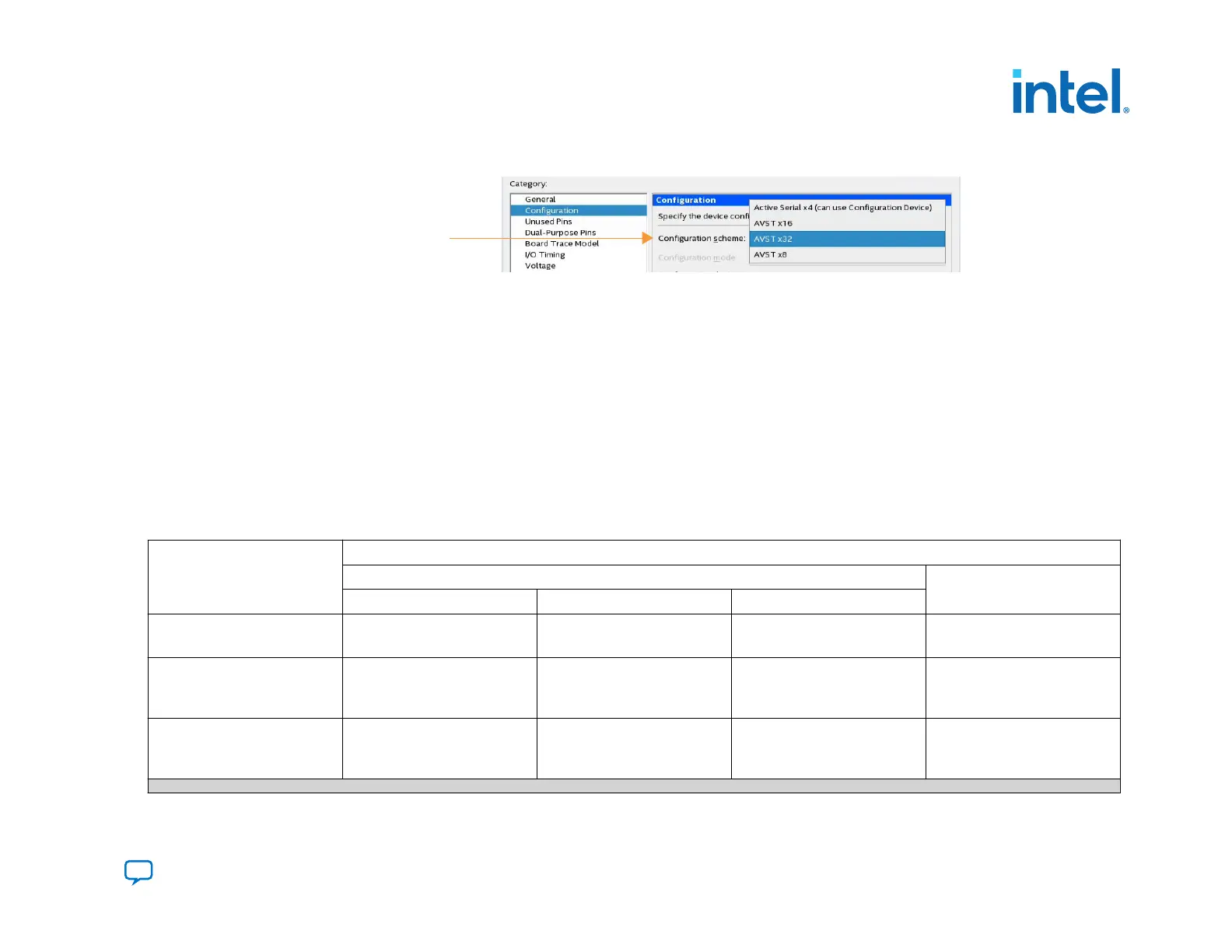

Figure 9. Specify Configuration Scheme to Specify MSEL Value

2.5.3. Device Configuration Pins for Optional Configuration Signals

All configuration schemes use the same dedicated pins for the standard control signals shown in the Intel Agilex Configuration

Timing Diagram. Many other optional configuration signals do not have dedicated pin assignments.

Device Configuration Pins without Fixed Assignments

Note:

Although the CONF_DONE and INIT_DONE configuration signals are not required, Intel recommends that you use these

signals as an indicator to ensure that configuration is successful. The SDM drives the CONF_DONE signal high after

successfully receiving full bitstream. The SDM drives the INIT_DONE signal high to indicate the device is fully in user mode.

These signals are important when debugging configuration.

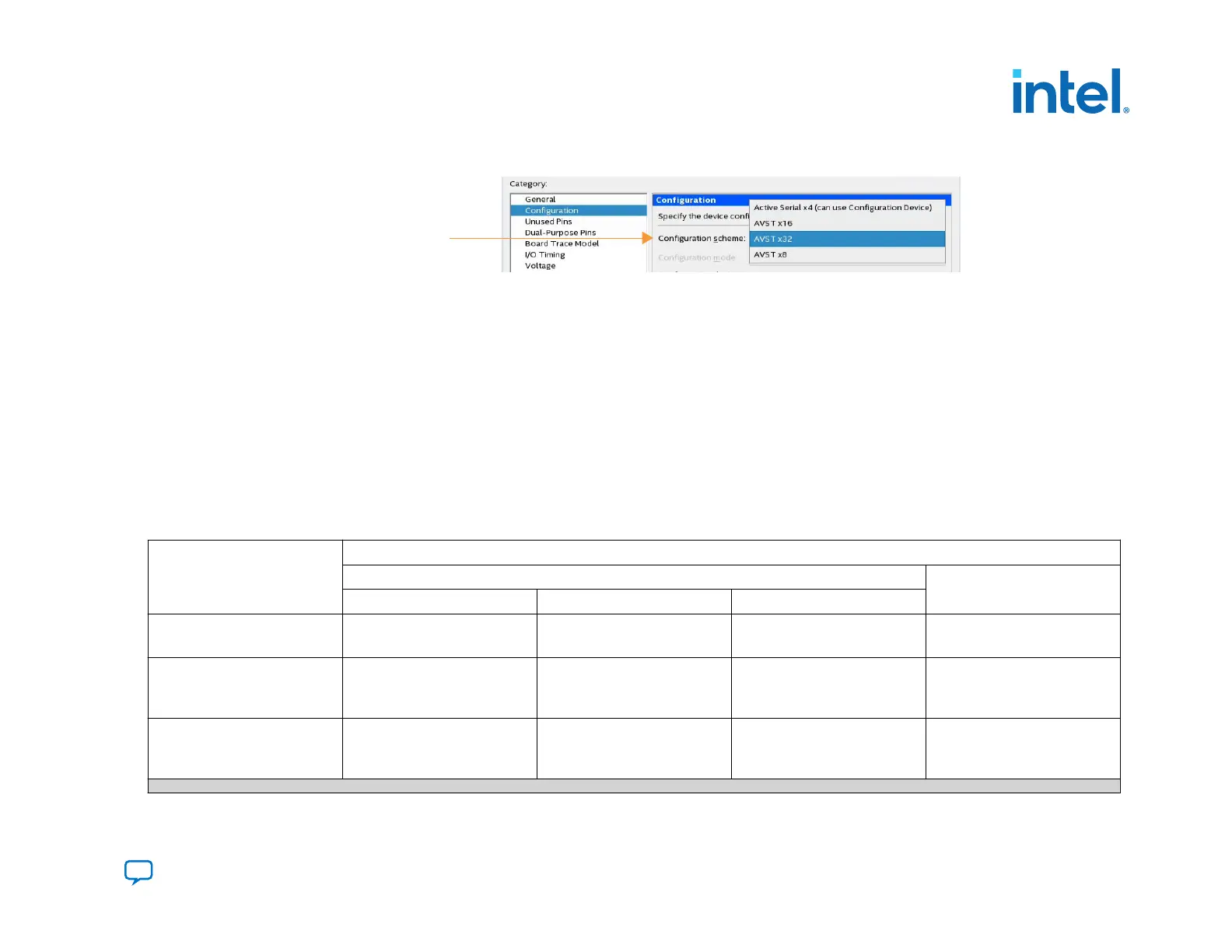

Table 6. Available SDM I/O Pin Assignments for Configuration Signals that Do Not Use Dedicated SDM I/O Pins

Signal Names

Configuration Scheme

Avalon-ST AS x4

x8 x16 x32

PWRMGT_SCL SDM_IO0 SDM_IO0

SDM_IO14

SDM_IO0

SDM_IO14

SDM_IO0

SDM_IO14

PWRMGT_SDA SDM_IO12

SDM_IO16

SDM_IO11

SDM_IO12

SDM_IO16

SDM_IO11

SDM_IO12

SDM_IO16

SDM_IO11

SDM_IO12

SDM_IO16

PWRMGT_ALERT SDM_IO0

SDM_IO9

SDM_IO12

SDM_IO0

SDM_IO9

SDM_IO12

SDM_IO0

SDM_IO12

SDM_IO0

SDM_IO12

continued...

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

31

Loading...

Loading...