3. Intel Agilex Configuration Schemes

3.1. Avalon-ST Configuration

The Avalon-ST configuration scheme replaces the FPP mode available in earlier device families. Avalon-ST is the fastest

configuration scheme for Intel Agilex devices. This scheme uses an external host, such as a microprocessor, MAX

®

II, MAX V,

or Intel MAX 10 device to drive configuration. The external host controls the transfer of configuration data from external

storage such as flash memory to the FPGA. The logic that controls the configuration process resides in the external host. You

can use the PFL II IP with a MAX II, MAX V, or Intel MAX 10 device as the host to read configuration data from the flash

memory device and configure the Intel Agilex device. The Avalon-ST configuration scheme is called passive because the

external host, not the Intel Agilex device, controls configuration.

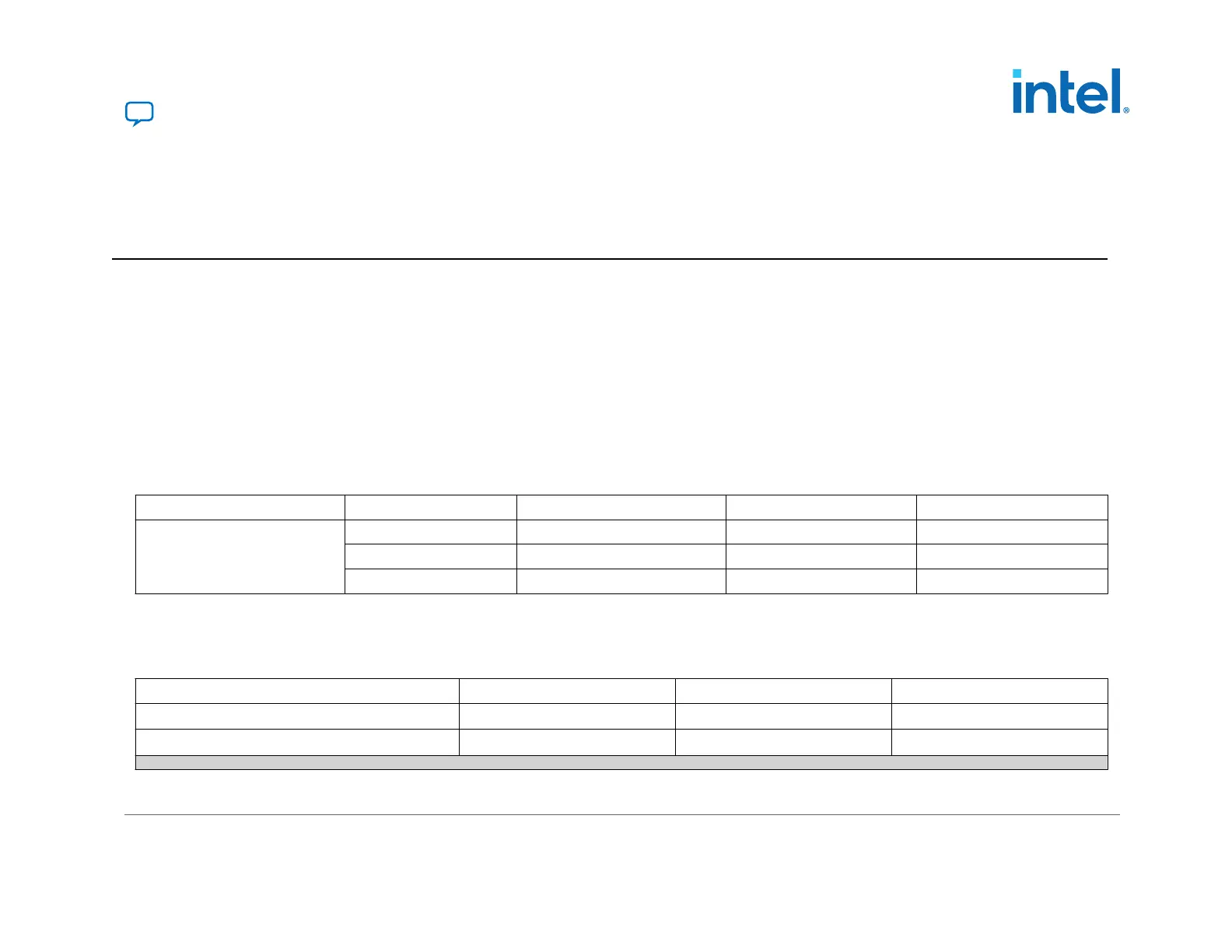

Table 14. Avalon-ST Configuration Data Width, Clock Rates, and Data Rates

Mbps is an abbreviation for Megabits per second.

Protocol Data Width (bits) Max Clock Rate Max Data Rate MSEL[2:0]

Avalon-ST

32 125 MHz 4000 Mbps 000

16 125 MHz 2000 Mbps 101

8 125 MHz 1000 Mbps 110

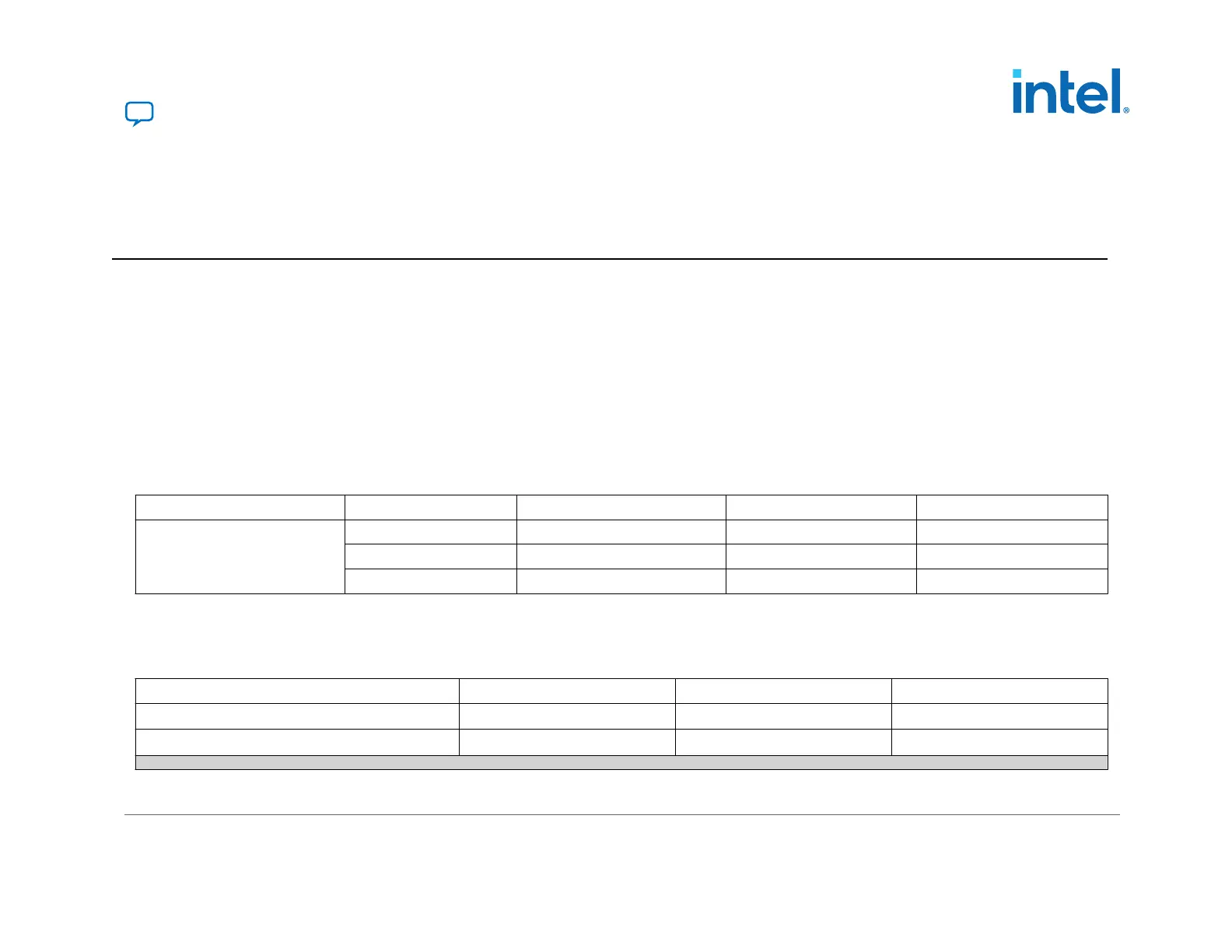

Table 15. Required Configuration Signals for the Avalon-ST Configuration Scheme

You can use an 8-, 16-, or 32-bit Avalon-ST configuration data bus. You specify SDM I/O pin functions using the Device ➤ Device and Pin Options ➤

Configuration dialog box in the Intel Quartus Prime software. For the Avalon-ST x16 and x32 configuration, you can reassign the GPIO, dual-purpose

configuration pins for other functions in user mode using the Device ➤ Device and Pin Options ➤ Dual-Purpose Pins dialog box.

Signal Name

Pin Type Direction Powered by

nSTATUS

SDM I/O Output V

CCIO_SDM

nCONFIG

SDM I/O Input V

CCIO_SDM

continued...

683673 | 2021.10.29

Send Feedback

Intel Corporation. All rights reserved. Intel, the Intel logo, and other Intel marks are trademarks of Intel Corporation or its subsidiaries. Intel warrants performance

of its FPGA and semiconductor products to current specifications in accordance with Intel's standard warranty, but reserves the right to make changes to any

products and services at any time without notice. Intel assumes no responsibility or liability arising out of the application or use of any information, product, or

service described herein except as expressly agreed to in writing by Intel. Intel customers are advised to obtain the latest version of device specifications before

relying on any published information and before placing orders for products or services.

*Other names and brands may be claimed as the property of others.

ISO

9001:2015

Registered

Loading...

Loading...