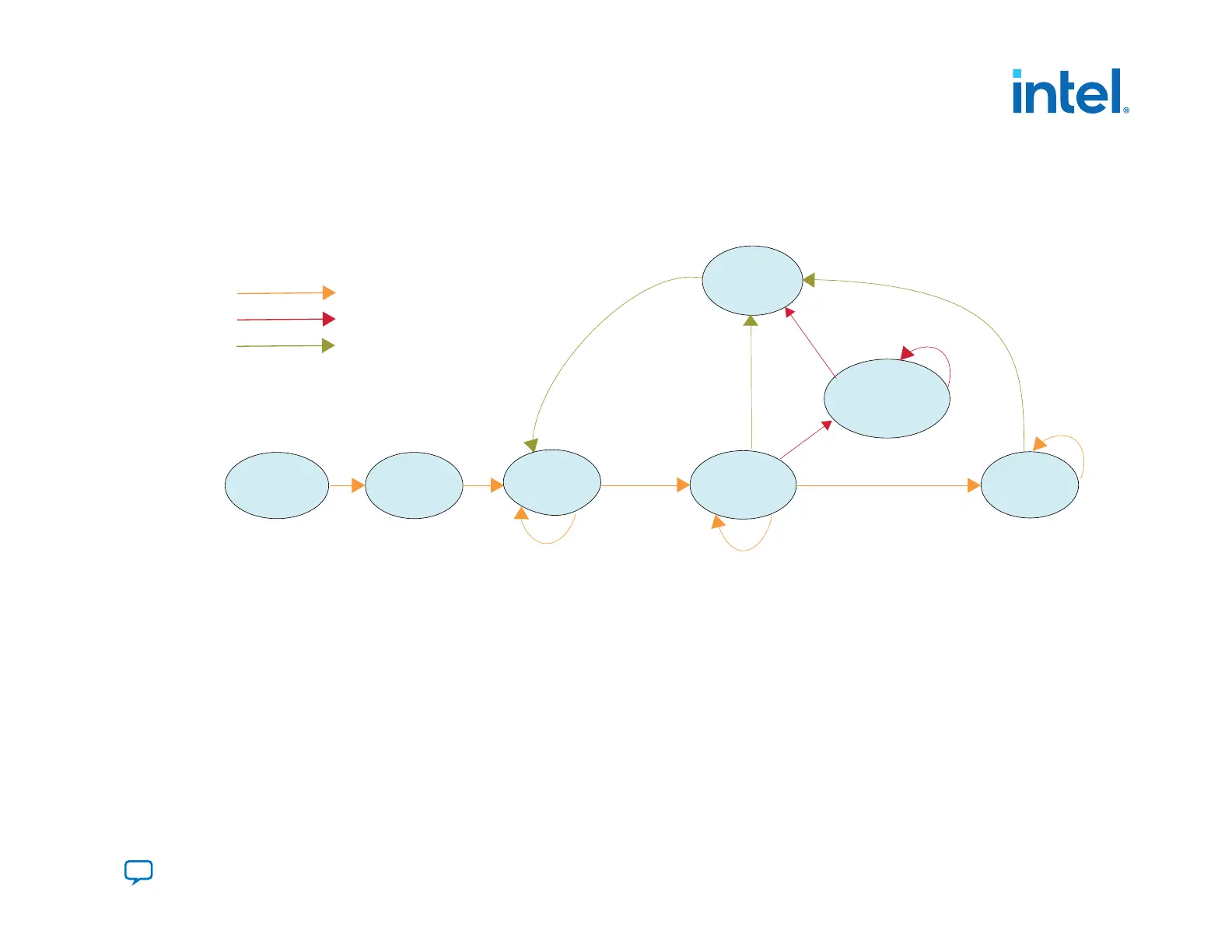

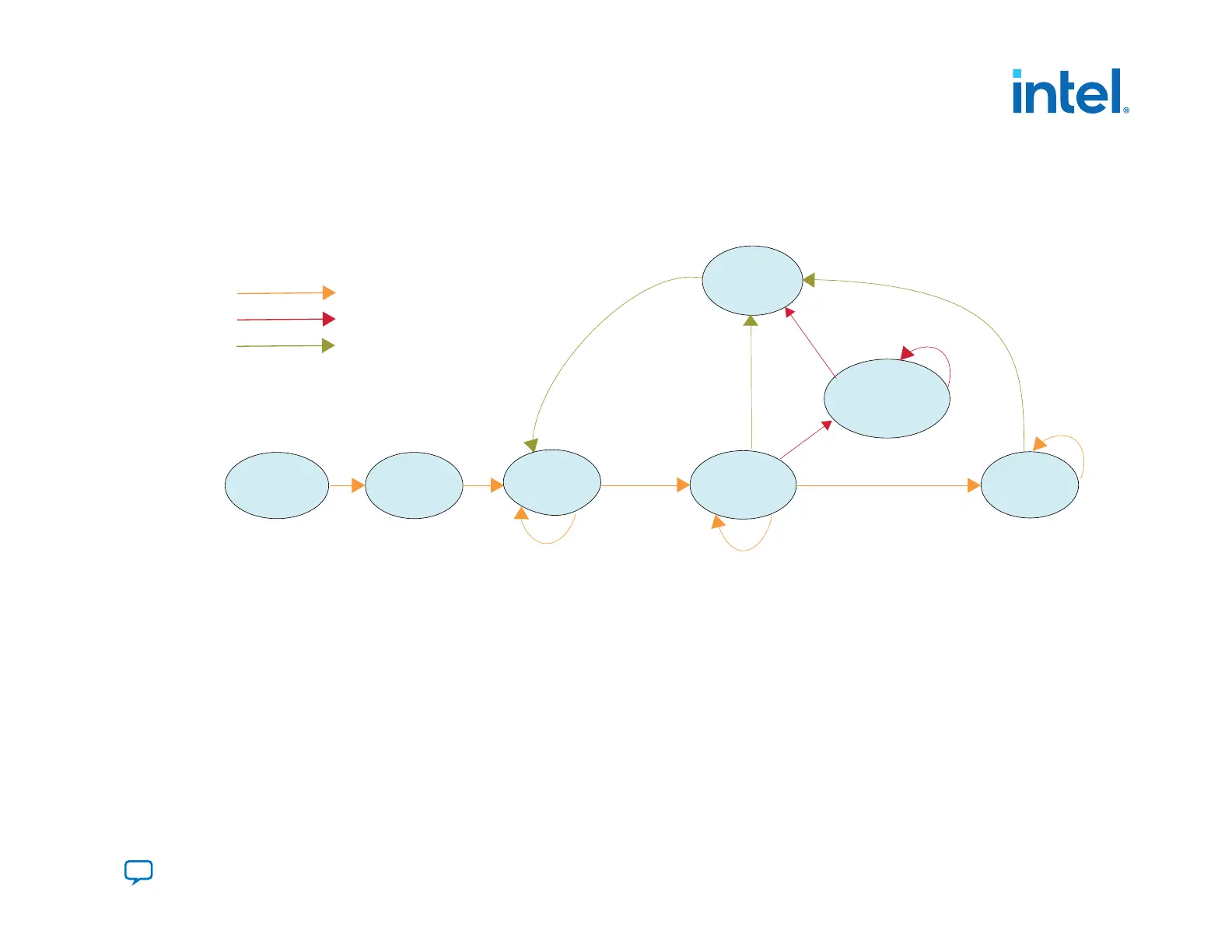

2.2. Configuration Flow Diagram

This topic describes the configuration flow for Intel Agilex devices.

Figure 7. Intel Agilex FPGA Configuration Flow

nCONFIG = LOW

Power-On

Idle

FPGA Config*

Failed FPGA Config

SDM

Startup

Device Clean

User

Mode

complete

Configuration pass

nCONFIG = LOW

nCONFIG = LOW

Device Clean

Configuration Pass Flow

Configuration Fail Flow

Reconfiguration Flow

nSTATUS= HIGH

nSTATUS = LOW

nSTATUS = HIGH

CONF_DONE = HIGH

INIT_DONE= HIGH

* FPGA first mode, fabric configuration begins immediately. HPS first mode, HPS configures the fabric.

** For nSTATUS low pulse duration, refer to the t STO parameter in the Intel Device Datasheet.

nCONFIG = HIGH

nSTATUS = HIGH

Configuration Error

nSTATUS = LOW Pulse**

nCONFIG = LOW

Initialization complete

nCONFIG = LOW

nCONFIG = HIGH

nCONFIG = HIGH

nCONFIG = HIGH

Note: You can perform JTAG configuration anytime from any state if the device is powered up and the power is intact. The Intel

Agilex device cancels the previous configuration and accepts the reconfiguration data from the JTAG interface. The nCONFIG

signal must be held in a stable state during JTAG configuration. A falling edge on the nCONFIG signal cancels the JTAG

configuration.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

23

Loading...

Loading...