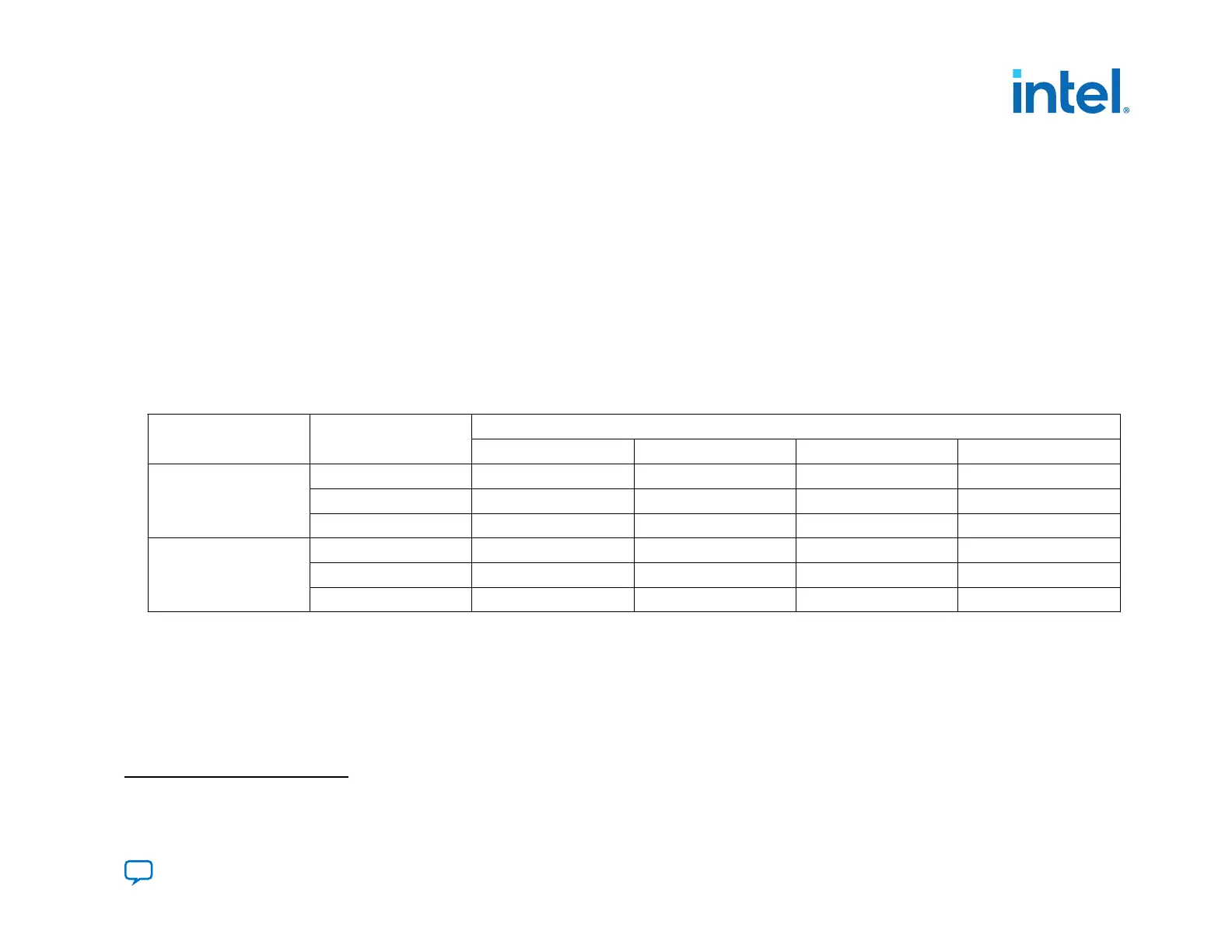

The following conditions were used to estimate the configuration time values:

• Set the VID mode of operation to PMBus Master mode

• Use Intersil ISL68137 regulator to regulate the PMBus

•

Set configuration clock source to OSC_CLK_1 with 25/100/125 MHz

• No advanced security features were enabled

•

For AVST x8/x16/x32 configuration modes, set the AVST_CLK to 125 MHz. The external host controller supplies the

AVST_DATA by asserting the AVST_VALID signal high whenever the AVST_READY signal is high.

•

For AS x4 configuration mode, set the AS_CLK to 166 MHz. Use a Micron device with a 2 Gb density range QSPI flash

memory.

Table 13. Configuration Time for Various Configuration Modes in P-tile designs

The data in this table is preliminary.

Device Bitstream File Size (MB) Configuration Time Estimation (ms)

AS x4

(8)

AVST x8 AVST x16 AVST x32

AGF 012

AGF 014

2.5 250 160 150 N/A

26 590 340 250 N/A

33 700 390 280 N/A

AGI 022

AGI 027

3.6 320 210 190 N/A

28 690 390 280 N/A

61 1,200 640 420 N/A

2.8. Generating Compressed .sof File

Intel Quartus Prime Pro Edition software allows you to generate a compressed .sof file. The compressed .sof file size is

smaller compared to the non-compressed .sof file.

To enable this option, go to Assignments ➤ Device ➤ Device and Pin Options ➤ General and check Generate

compressed sof checkbox. By default, the option is disabled.

(8)

For non-Micron QSPI flash memory, the AS x4 configuration time increases by 126 ms.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

51

Loading...

Loading...