4. Click OK to confirm and close the Device and Pin Options.

2.6.2. OSC_CLK_1 Clock Input

OSC_CLK_1 Requirements

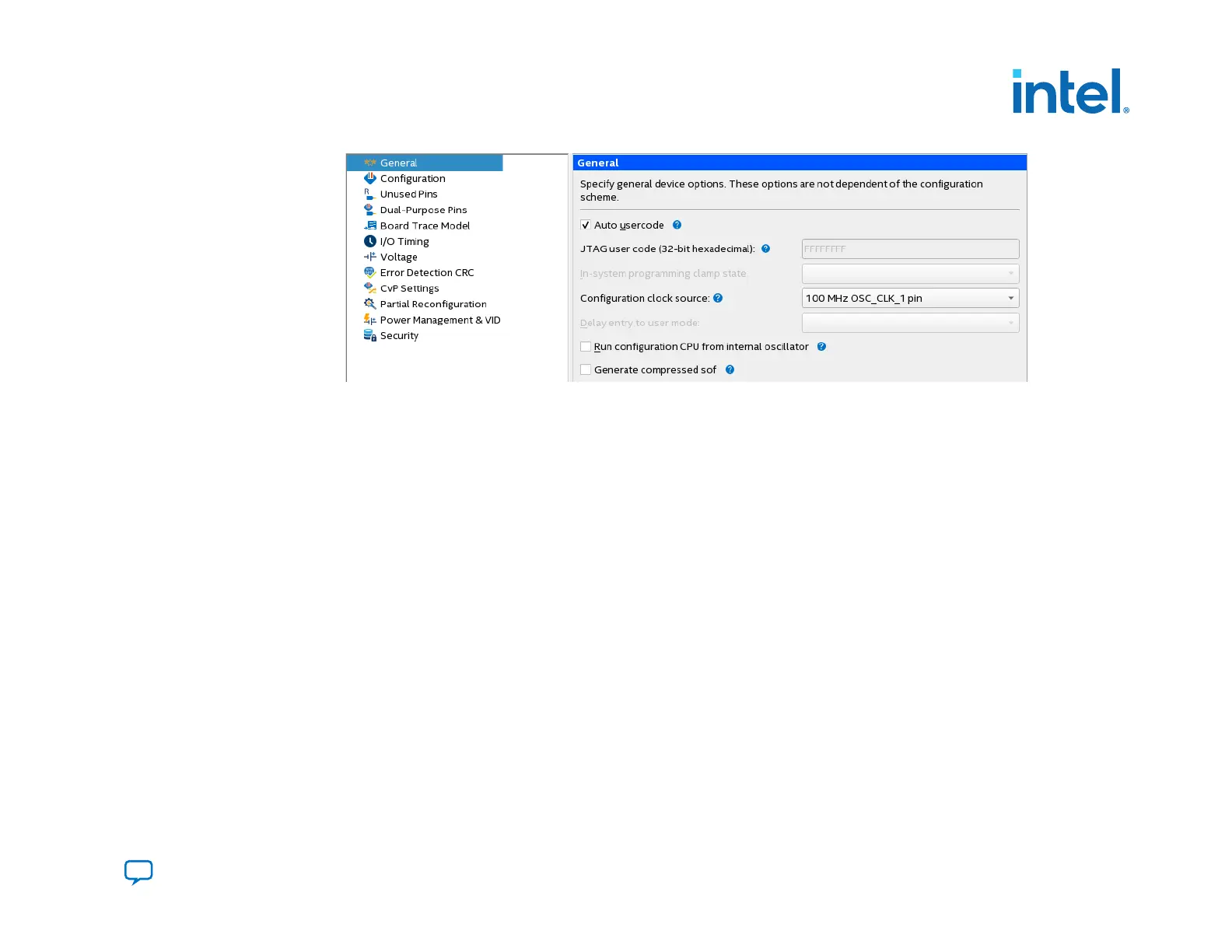

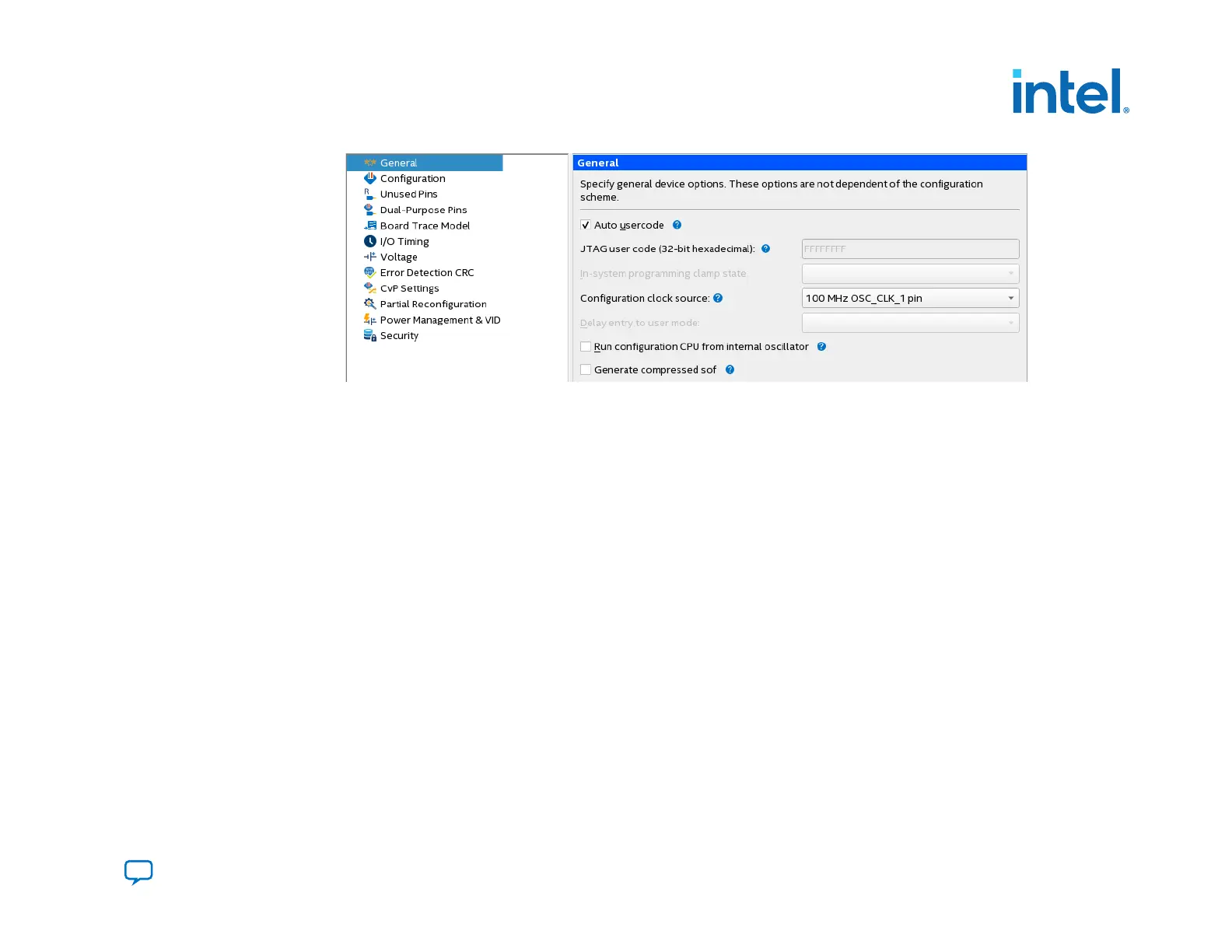

When you drive the OSC_CLK_1 input clock with an external clock source and enable OSC_CLK_1 in the Intel Quartus Prime

software, the device loads the majority of the configuration bitstream at 250 MHz. Intel Agilex devices include an internal

oscillator in addition to OSC_CLK_1 which runs the configuration process at a frequency between 160-230 MHz. Intel Agilex

devices always use this internal oscillator to load the first section of the bitstream, up to a maximum of 512 kilobyte (KB).

The SDM can use either clock source for the remainder of device configuration. If you use the internal oscillator, you can leave

the OSC_CLK_1 unconnected. If you use transceivers, you must provide an external clock to this pin.

When you specify OSC_CLK_1 for configuration, the OSC_CLK_1 clock must be a stable and free-running clock.

When you specify AS configuration scheme and nCONFIG is pull high, the SDM starts the configuration once the device exits

the POR state. Ensure the OSC_CLK_1 clock is available before SDM starts to load the bitstream from the quad SPI flash or

you need to supply a stable free-running clock before/at the same time V

CCIO_SDM

ramps up to the typical voltage level.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

49

Loading...

Loading...