Avalon-ST x8 configuration scheme uses the SDM pins only. Avalon-ST x16 and x32 configuration scheme only use dual-

purpose I/O pins that you can use as general-purpose I/O pins after configuration.

Related Information

• Avalon Interface Specifications

• Avalon-ST Configuration Timing

For Avalon-ST Timing Parameters for Configuration in Intel Agilex Devices.

3.1.4. RBF Configuration File Format

If you do not use the Parallel Flash Loader II Intel FPGA IP core to program the flash, you must generate the .rbf file.

The data in .rbf file are in little-endian format

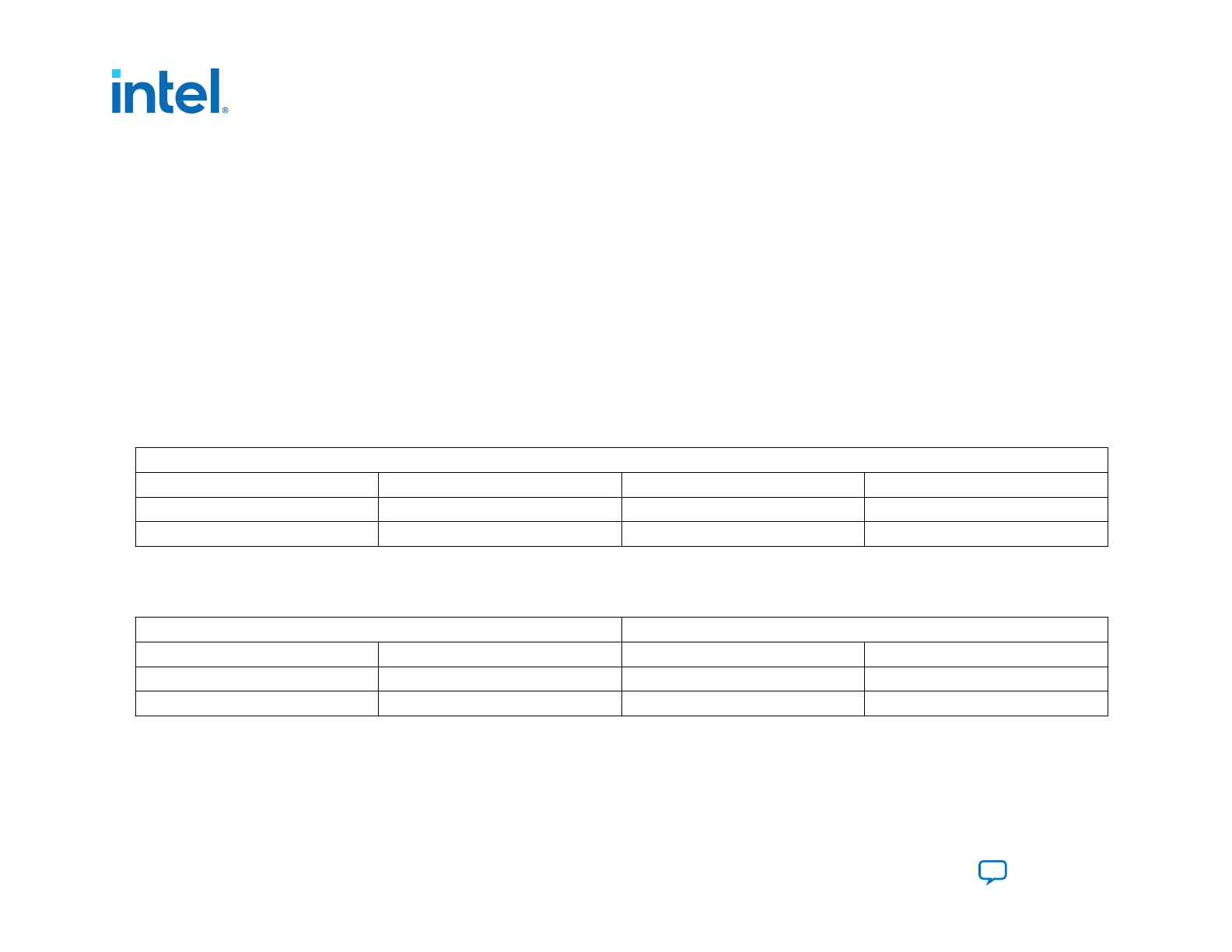

Table 17. Writing 32-bit Data

For a x32 data bus, the first byte in the file is the least significant byte of the configuration double word, and the fourth byte is the most significant byte.

Double Word = 01EE1B02

LSB: BYTE0 = 02 BYTE1 = 1B BYTE2 = EE MSB: BYTE3 = 01

D[7:0] D[15:8] D[23:16] D[31:24]

0000 0010 0001 1011 1110 1110 0000 0001

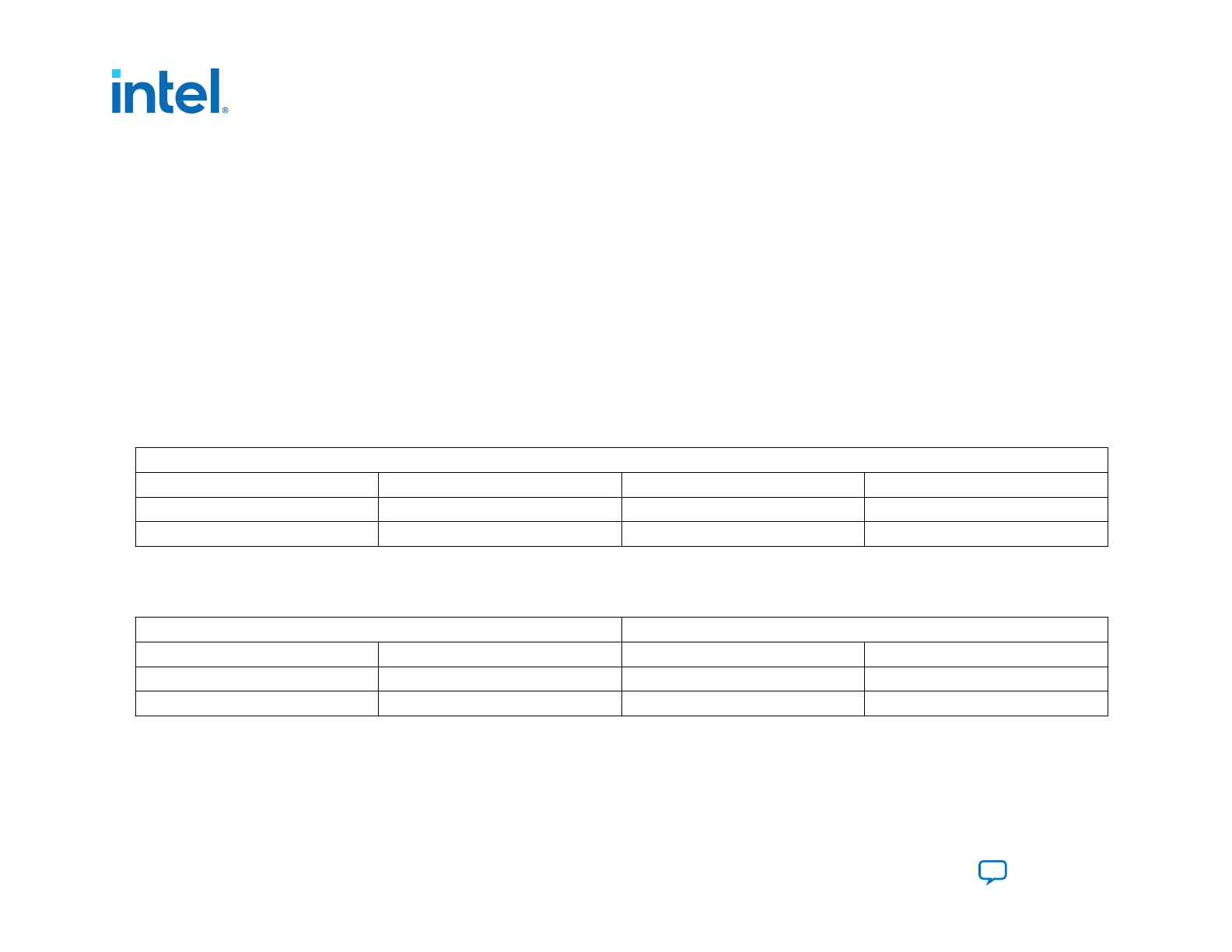

Table 18. Writing 16-bit Data

For a x16 data bus, the first byte in the file is the least significant byte of the configuration word, and the second byte is the most significant byte of the

configuration word.

WORD0 = 1B02

WORD1 = 01EE

LSB: BYTE0 = 02 MSB: BYTE1 = 1B LSB: BYTE2 = EE MSB: BYTE3 = 01

D[7:0] D[15:8] D[7:0] D[15:8]

0000 0010 0001 1011 1110 1110 0000 0001

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

60

Loading...

Loading...