•

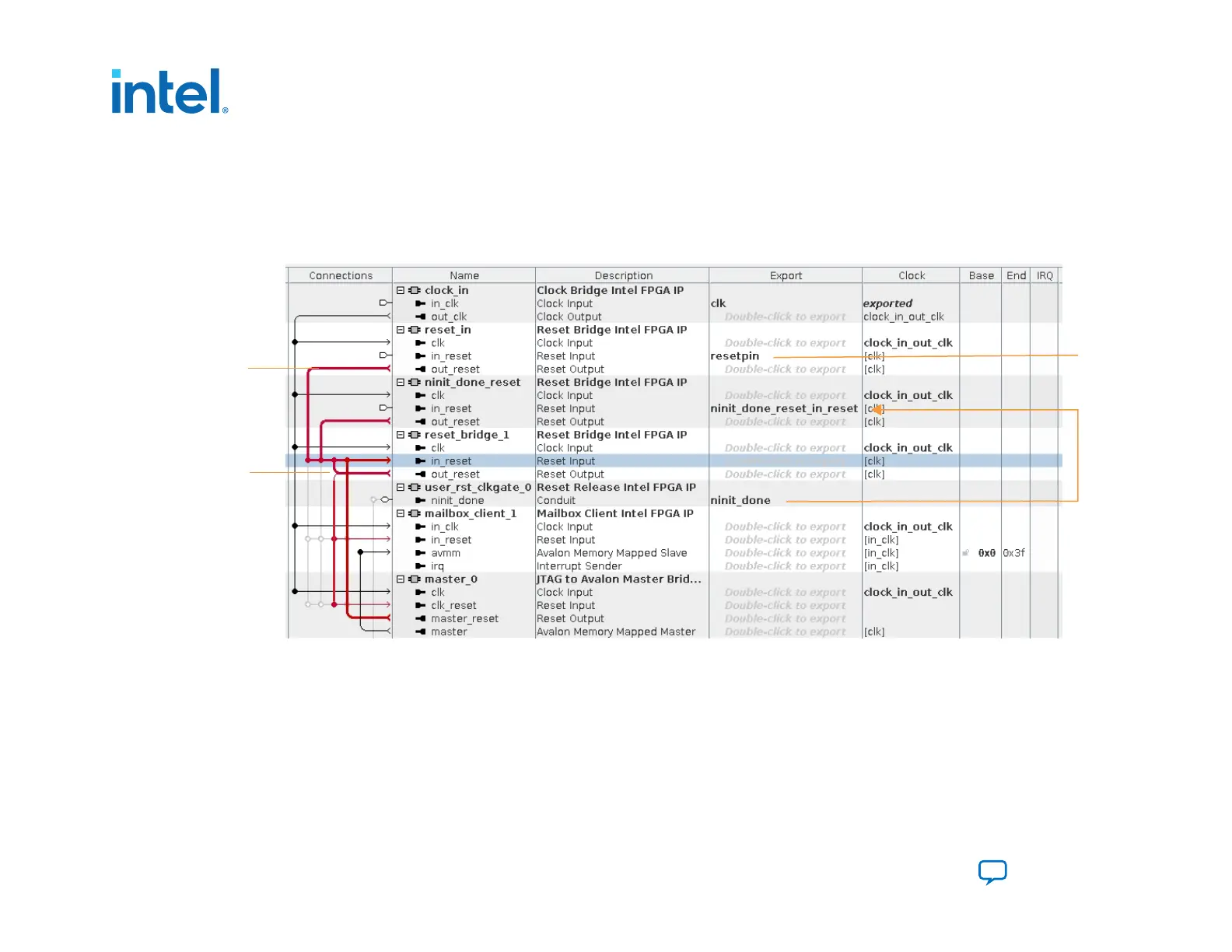

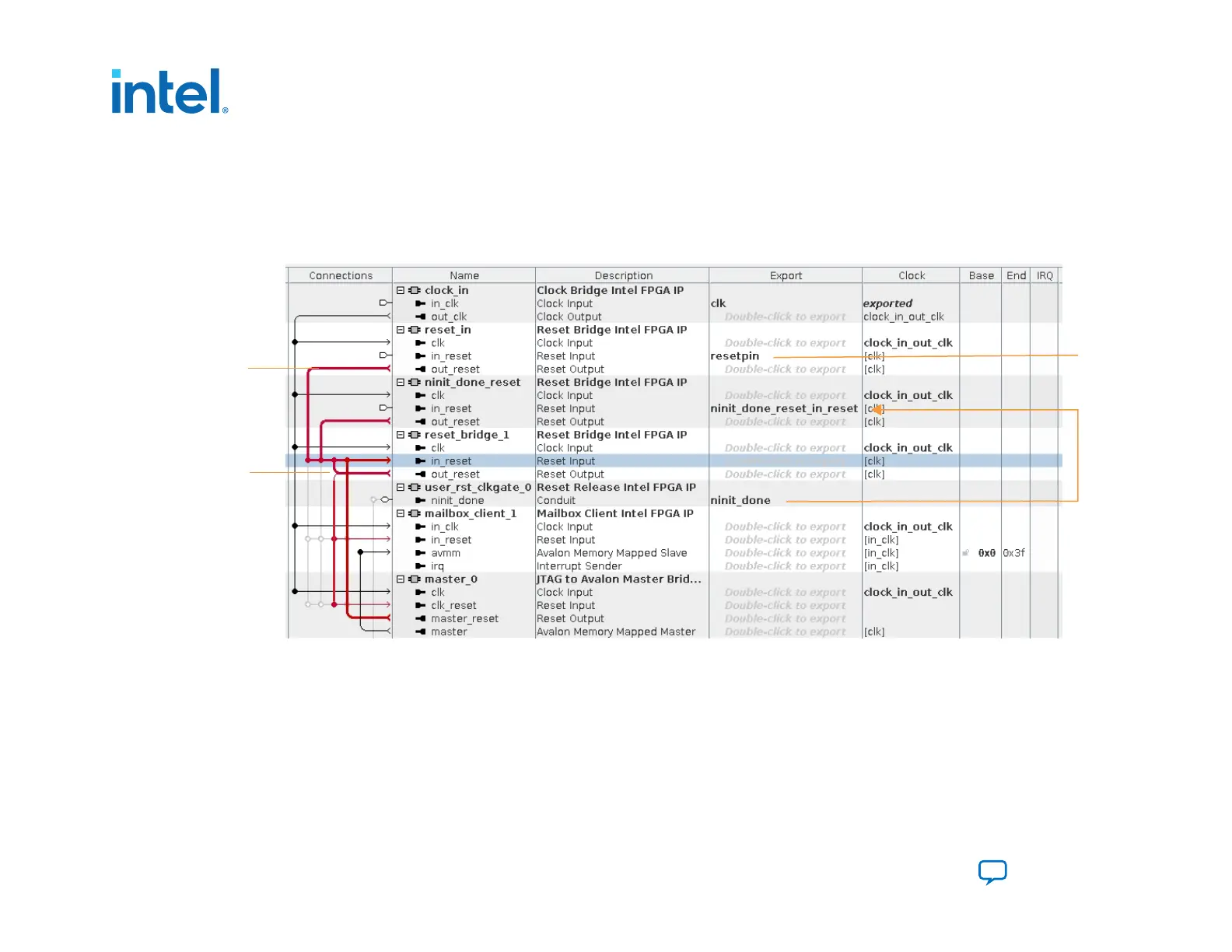

The ninit_done output signal from Reset Release IP gates this reset by connecting to the ninit_done_reset

in_reset pin.

•

The reset_in Reset Bridge Intel FPGA IP provides a user mode reset. In this design, the exported resetpin connects

to application logic.

•

Figure 76. Required Communication and Host Components for the Remote System Update Design Example

PCB

Connection

User Mode

Reset

User Mode

Reset

Power On

Reset

5.6.2. Creating Initial Flash Image Containing Bitstreams for Factory Image and One Application

Image

1. On the File menu, click Programming File Generator.

2. Select Intel Agilex from the Device family drop-down list.

3. Select the configuration mode from the Configuration mode drop-down list. The current Intel Quartus Prime Software

only supports remote system update feature in Active Serial x4.

5. Remote System Update (RSU)

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

196

Loading...

Loading...