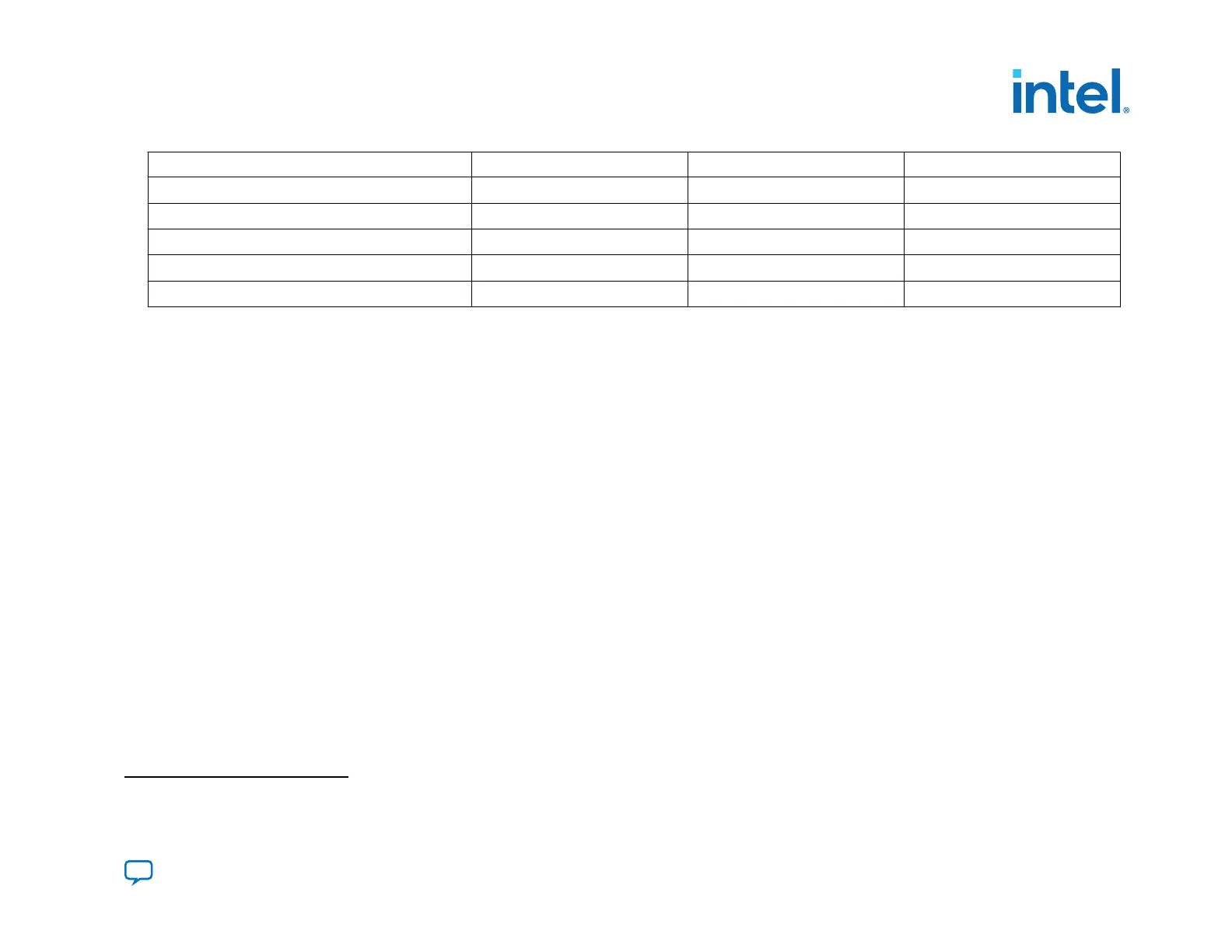

Configuration Function Pin Type Direction Powered by

MSEL[2:0]

SDM I/O Input V

CCIO_SDM

AS_nCSO[3:0]

SDM I/O Output V

CCIO_SDM

AS_DATA[3:0]

SDM I/O Bidirectional V

CCIO_SDM

AS_CLK

SDM I/O Output V

CCIO_SDM

AS_nRST

(12)

SDM I/O Output V

CCIO_SDM

Note:

Although the CONF_DONE and INIT_DONE configuration signals are not required, Intel recommends that you use these

signals. The SDM drives the CONF_DONE signal high after successfully receiving full bitstream. The SDM drives the

INIT_DONE signal high to indicate the device is fully in user mode.These signals are important when debugging configuration.

MSEL Pin Function for the AS x4 Configuration Scheme

The SDM samples the MSEL pins immediately after power-on in the SDM Start state. After the SDM samples the MSEL pins,

the MSEL pins become active-low chips selects. For AS x4 designs using one flash device, AS_nCSOO asserts low when the

SDM starts to communicate with the QSPI flash. The remaining chip select pins, AS_nCSO1 - AS_nCSO3 deassert high.

Related Information

• AS Configuration Timing in Intel Agilex Devices

For timing parameter minimum, typical, and maximum values.

• Intel Agilex Power Management User Guide

3.2.1. AS Configuration Scheme Hardware Components and File Types

You use the following components to implement the AS configuration scheme:

• Quad SPI flash memory

• The Intel FPGA Download Cable II to connect the Intel Quartus Prime Programmer to the PCB.

(12)

Even if not currently utilized, connect the pin to ensure future compatibility.

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

103

Loading...

Loading...