2.3. Device Response to Configuration and Reset Events

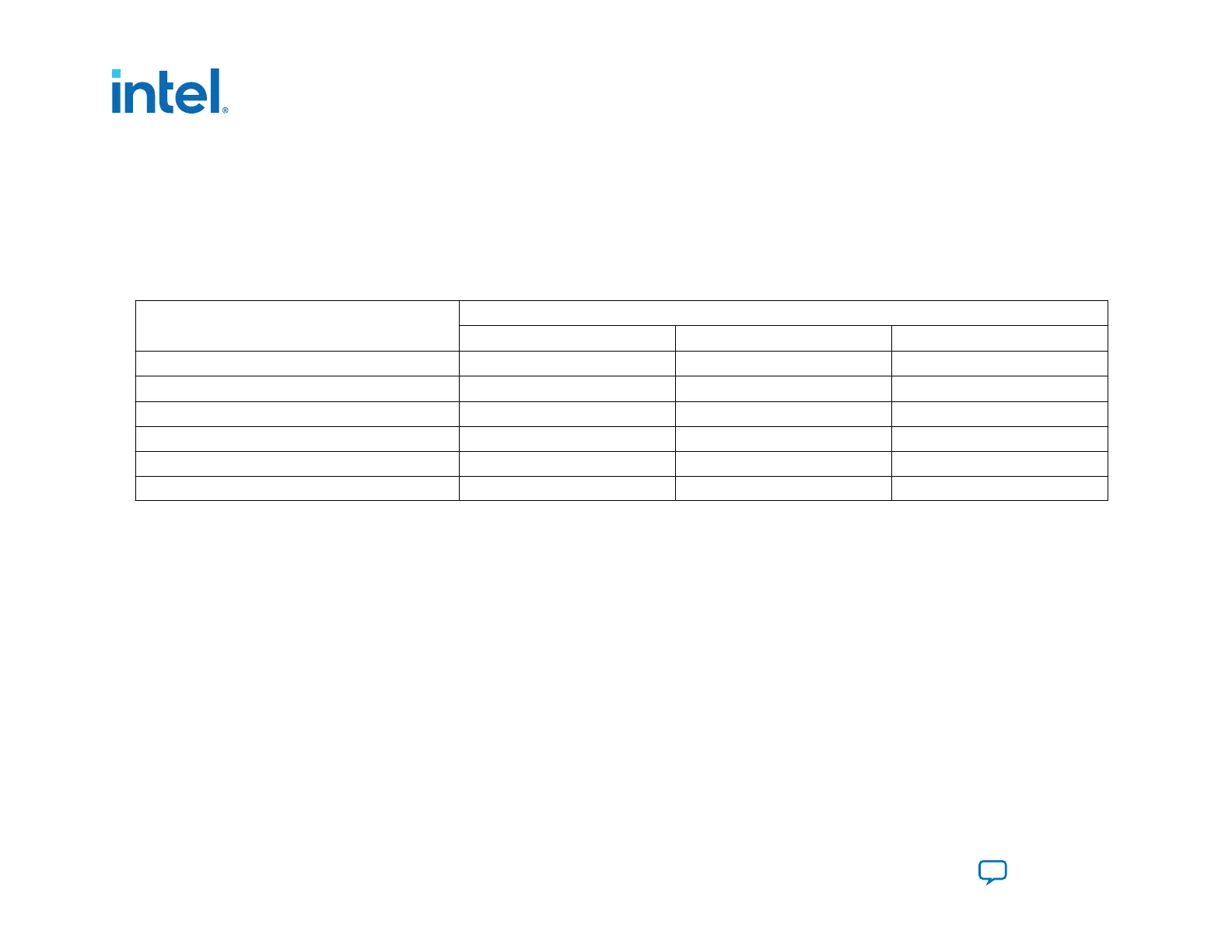

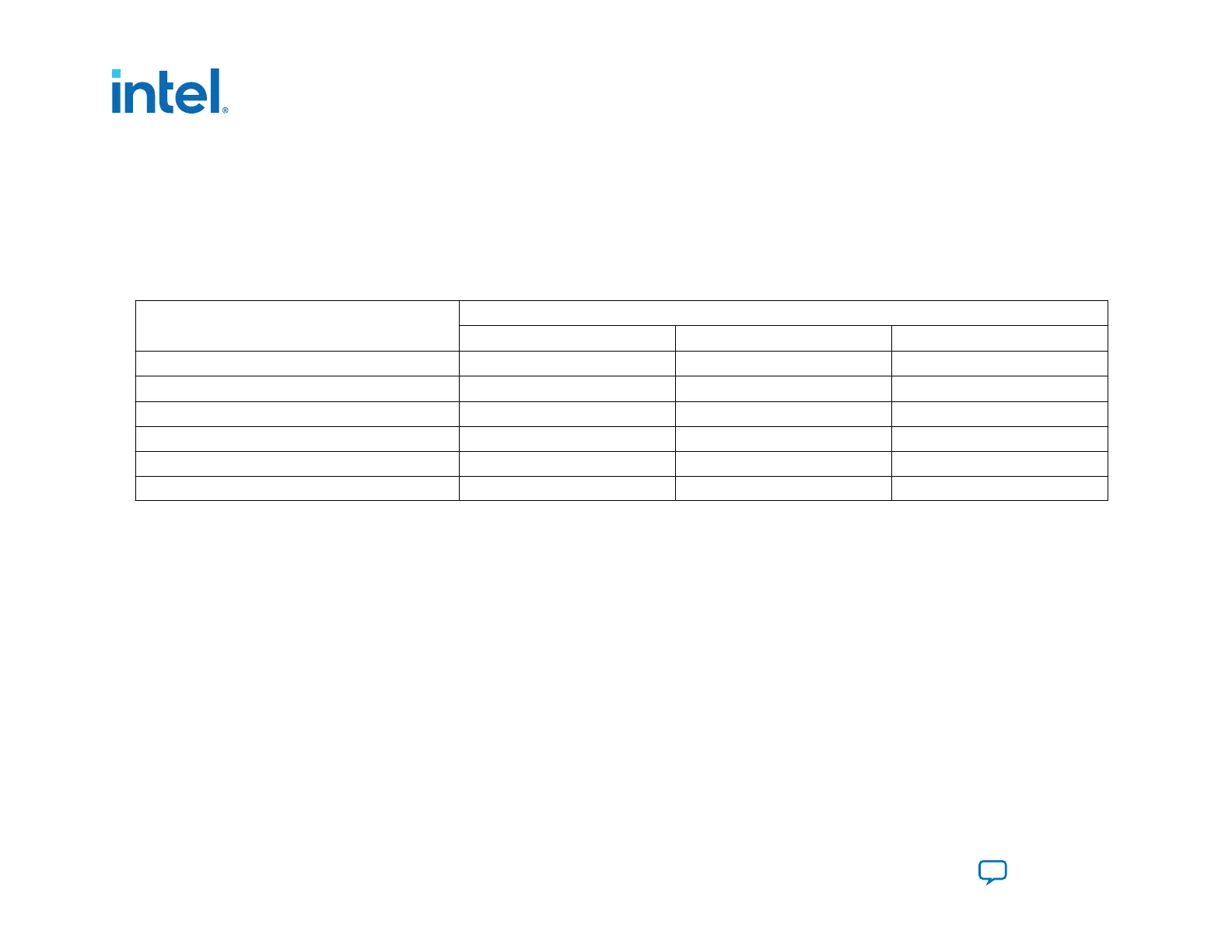

The following table summarizes the device response to various external configuration and reset events.

Note:

HPS_COLD_nRESET is a SDM input pin that manages the HPS reset.

Table 3. Device Response Due To Configuration and Reset Events

Events marked by a tick (√) require reset initiated by provided reset type.

Action Reset Type

Power Cycle

nCONFIG HPS_COLD_nRESET

Wipe the FPGA √ √ —

Sample MSEL pins

√ — —

Read fuses √ — —

Run the SDM boot ROM code √ — —

Reset the SDM √ — —

Reset the HPS √ √ √

Note: When using QSPI, you can use Remote System Update (RSU) to load a specific image with the same device responses as

nCONFIG.

Related Information

Intel Agilex Power Management User Guide

2.4. Additional Clock Requirements for HPS and Transceivers

The Intel Agilex device has specific clock requirements for transceivers and HPS EMIF IP. These clock requirements must be

met before the FPGA configuration begins.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

26

Loading...

Loading...