Note: Intel Agilex devices using Avalon ST x32 configuration and DDR x72 external memory interfaces are limited to a maximum of

three memory interfaces. The Avalon ST x8 and x16 can support up to four DDR x72 external memory interfaces.

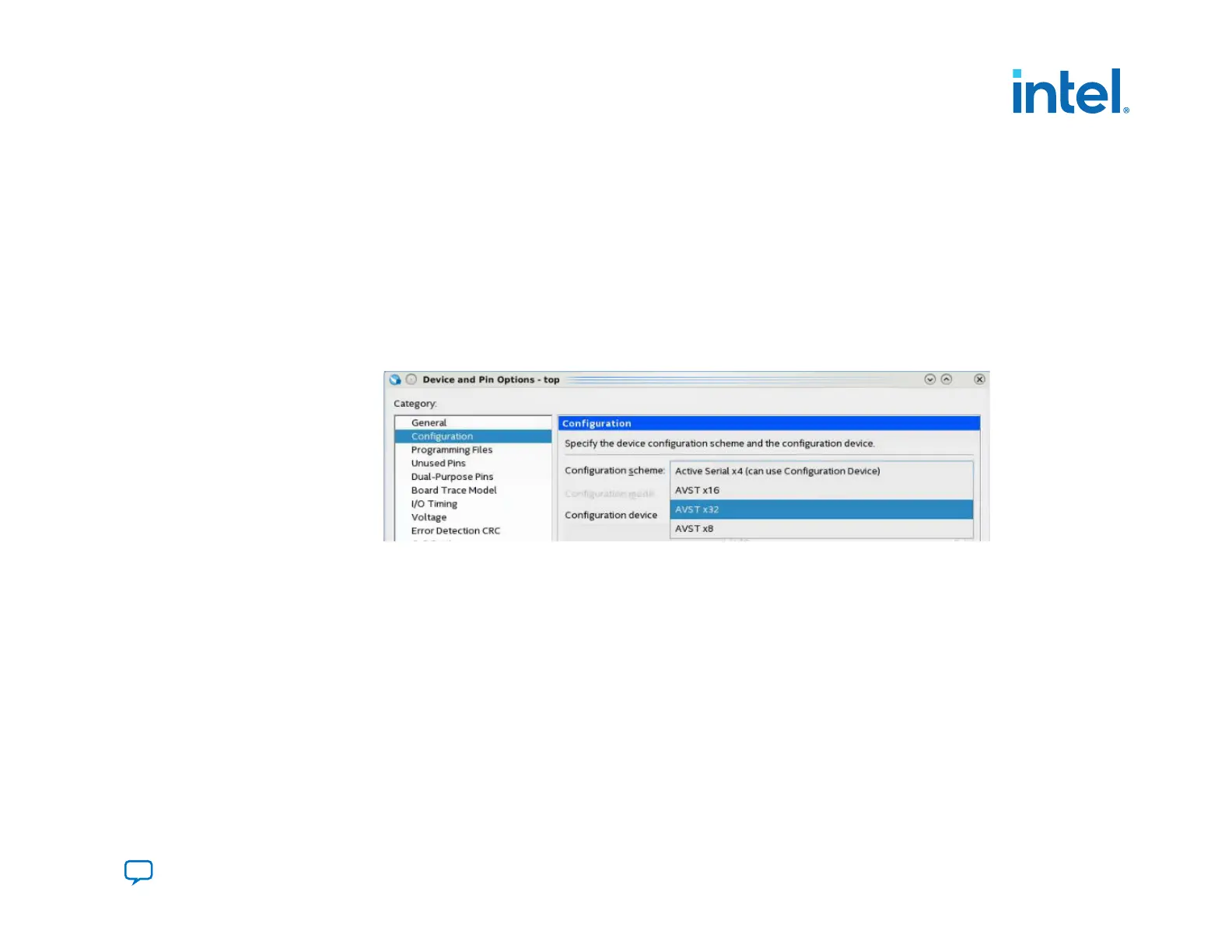

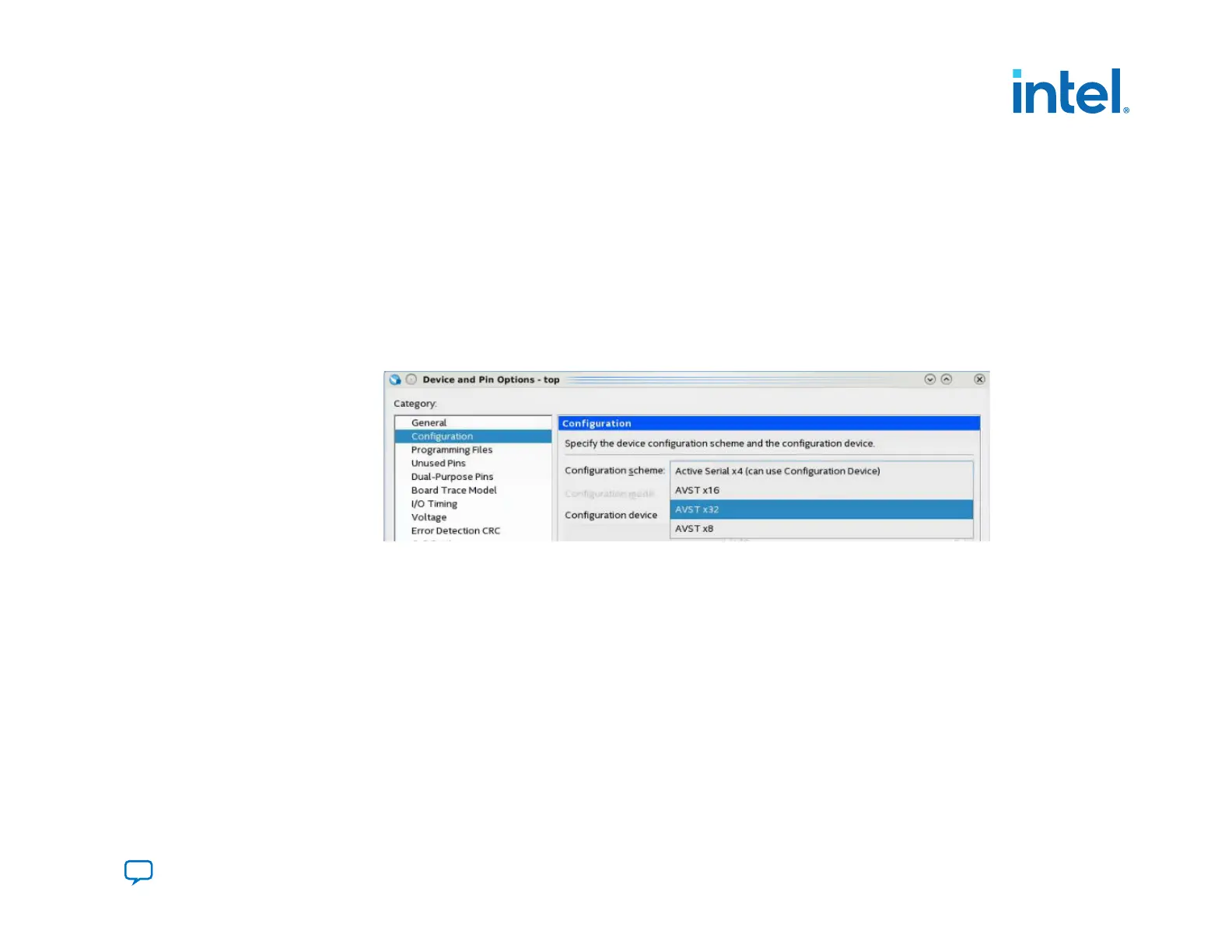

3.1.2. Enabling Avalon-ST Device Configuration

You enable the Avalon-ST device configuration scheme in the Intel Quartus Prime software.

Complete the following steps to specify an Avalon-ST interface for device configuration.

1. On the Assignments menu, click Device.

2. In the Device and Pin Options dialog box, select the Configuration category.

3. In the Configuration window, in the Configuration scheme dropdown list, select the appropriate Avalon-ST bus width.

4. Click OK to confirm and close the Device and Pin Options dialog box.

3.1.3. The AVST_READY Signal

Before beginning configuration, trigger device cleaning by toggling the nCONFIG pin from high to low to high. This nCONFIG

transition also returns the device to the configuration state.

If you use the Parallel Flash Loader II Intel FPGA IP core as the configuration host, the AVST_READY synchronizer logic is

included.

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

57

Loading...

Loading...