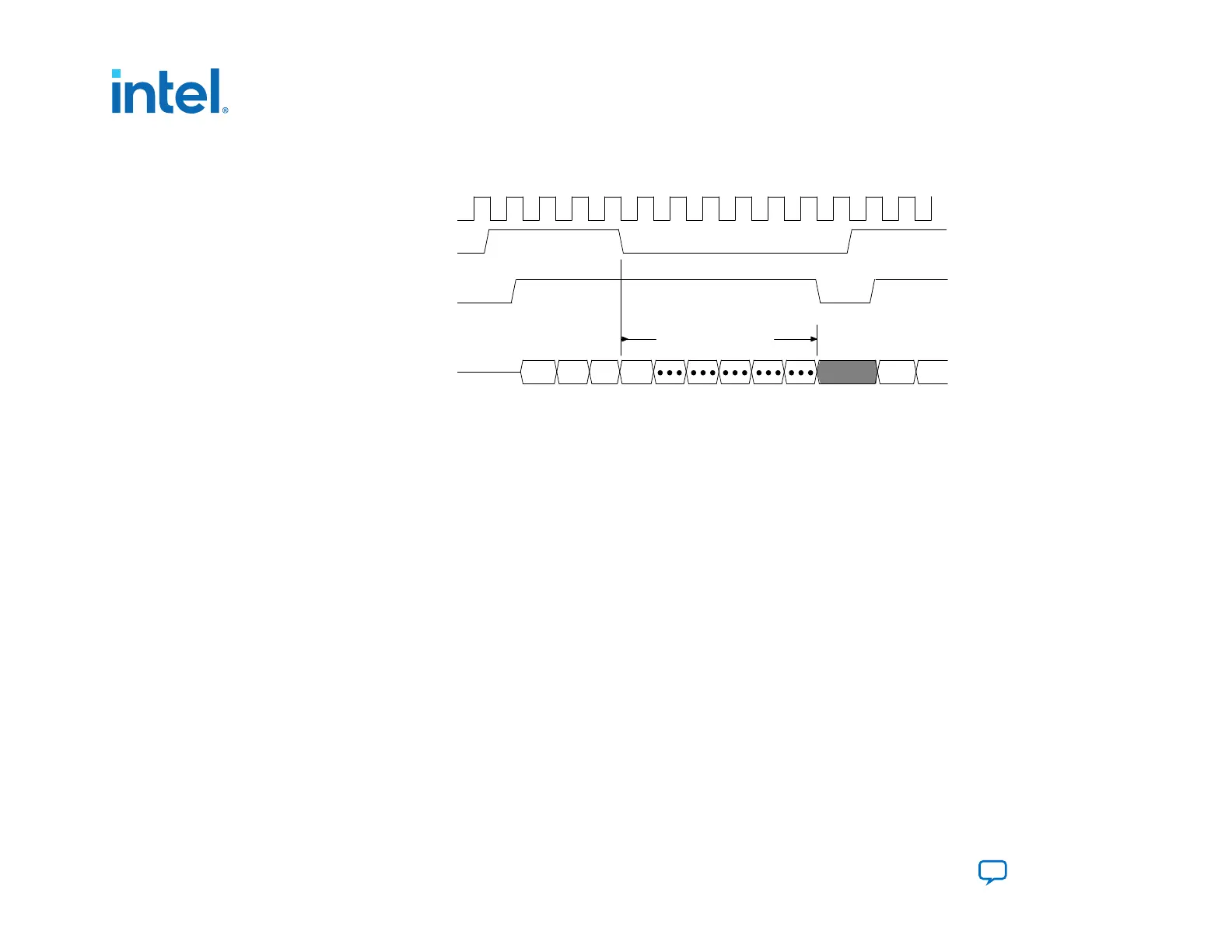

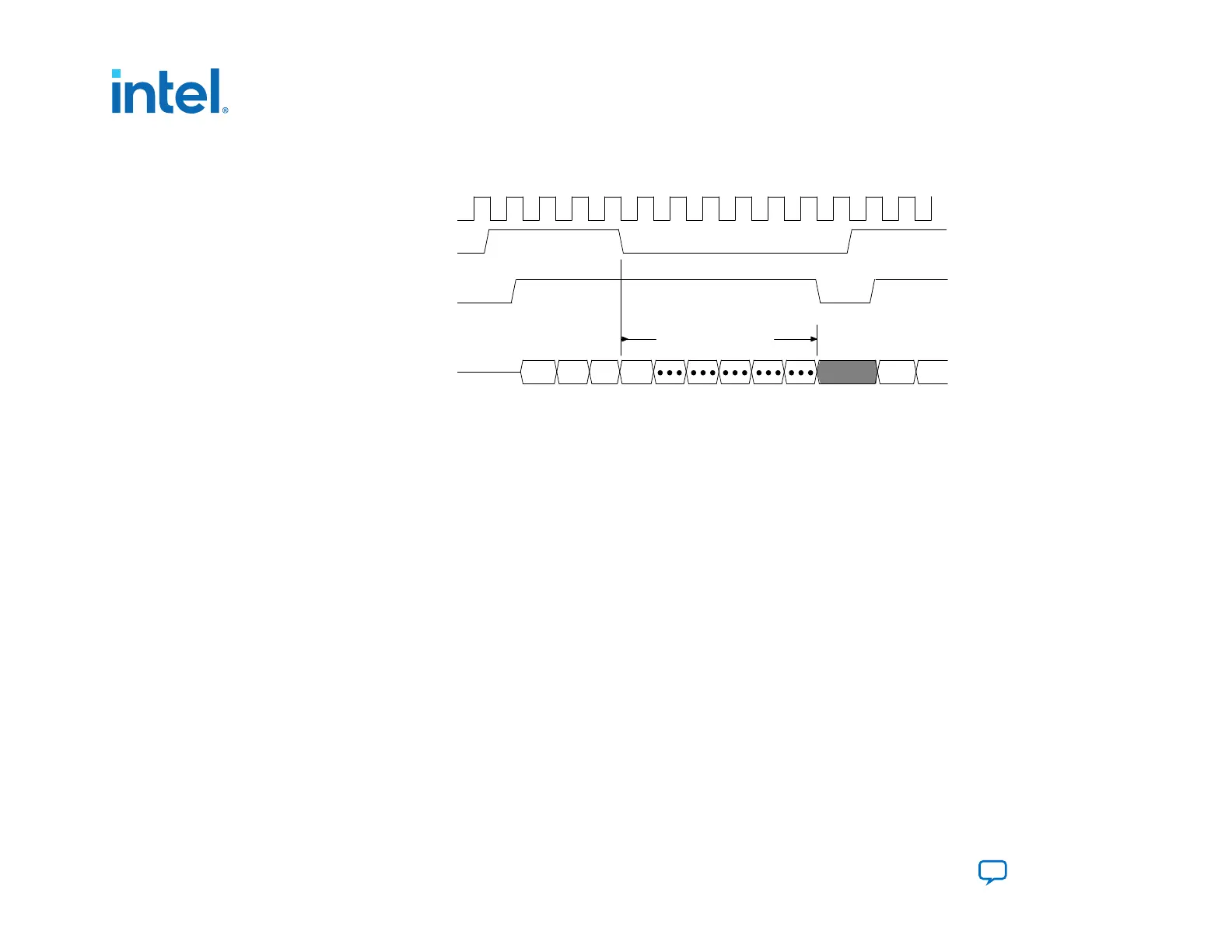

Figure 16. Monitoring the AVST_READY Signal and Responding to Backpressure

AVST_CLK

AVSTx8_READY

or AVST_READY

AVSTx8_VALID

or AVST_VALID

AVSTx8_DATA[7:0

AVST_DATA[15:0]

AVST_data[31:0]]

must send no more

than 6 valid clocks after

ready goes low

data0 data1 data2 data3

The configuration files for Intel Agilex devices can be highly compressed. During configuration, the decompression of the bit

stream inside the device requires the host to pause before sending more data. The Intel Agilex device asserts the

AVST_READY signal when the device is ready to accept data. The AVST_READY signal is only valid when the nSTATUS pin is

high. In addition, the host must handle backpressure by monitoring the AVST_READY signal and may assert AVST_VALID

signal any time after the assertion of AVST_READY signal. The host must monitor the AVST_READY signal throughout the

configuration.

Note:

To receive a valid nSTATUS response from the device, your host must only monitor this signal after the device power group 3

is powered up to the recommended operating condition and after the maximum POR delay specification is met. For more

information, refer to the POR delay specification in Intel Agilex Device Data Sheet.

Note: For Avalon-ST x16 and x32, after Power-On-Reset you must not send data to the device until it indicates it is ready using

nSTATUS. You must drive nCONFIG low and wait for nSTATUS to go low. Next, you should drive nCONFIG high and wait for

nSTATUS to go high. The device can starting sending data when AVST_READY asserts.

3. Intel Agilex Configuration Schemes

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

58

Loading...

Loading...