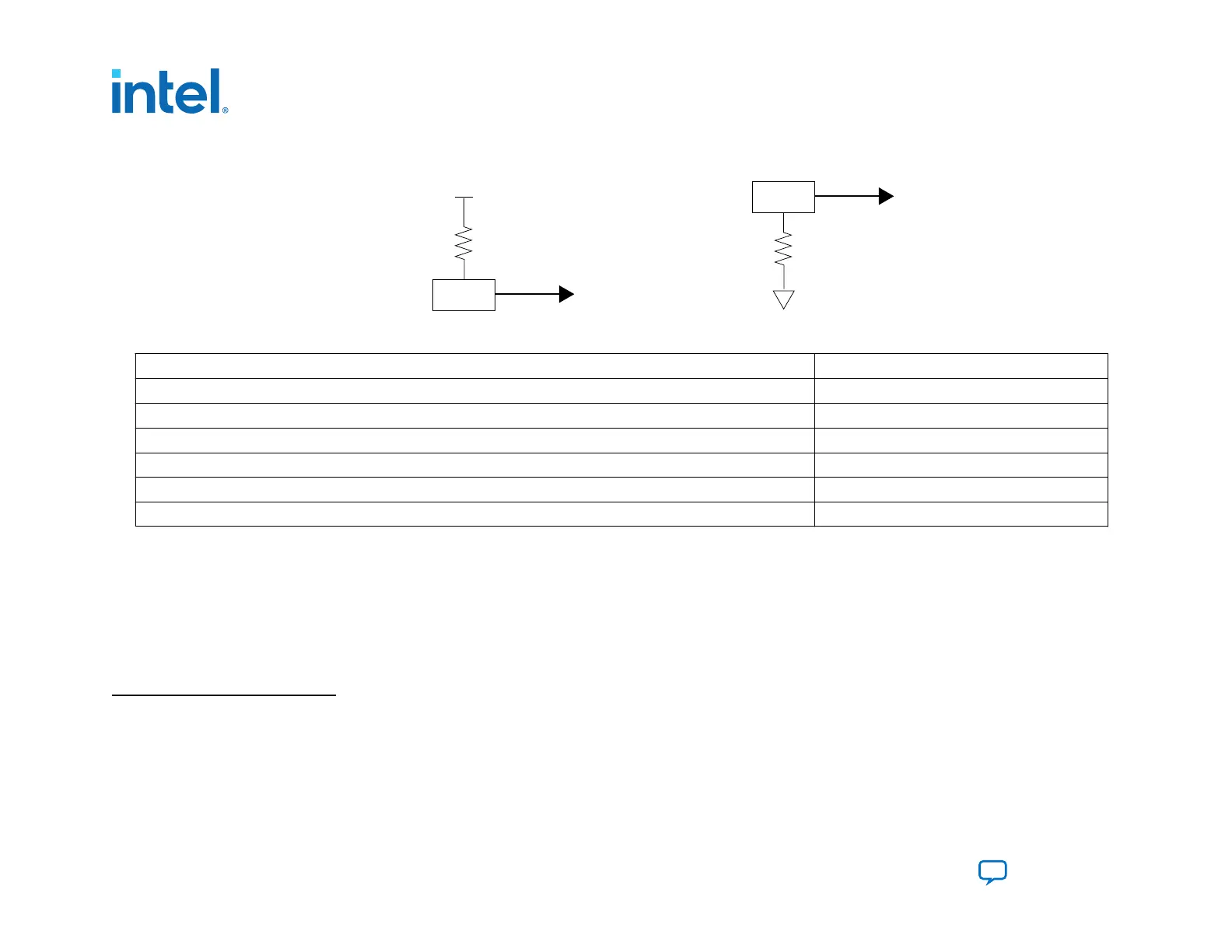

Figure 8. MSEL Pull-Up and Pull-Down Circuit Diagram

RUP

VCCIO_SDM

MSEL

4.7kΩ

RDN

MSEL

4.7kΩ

OR

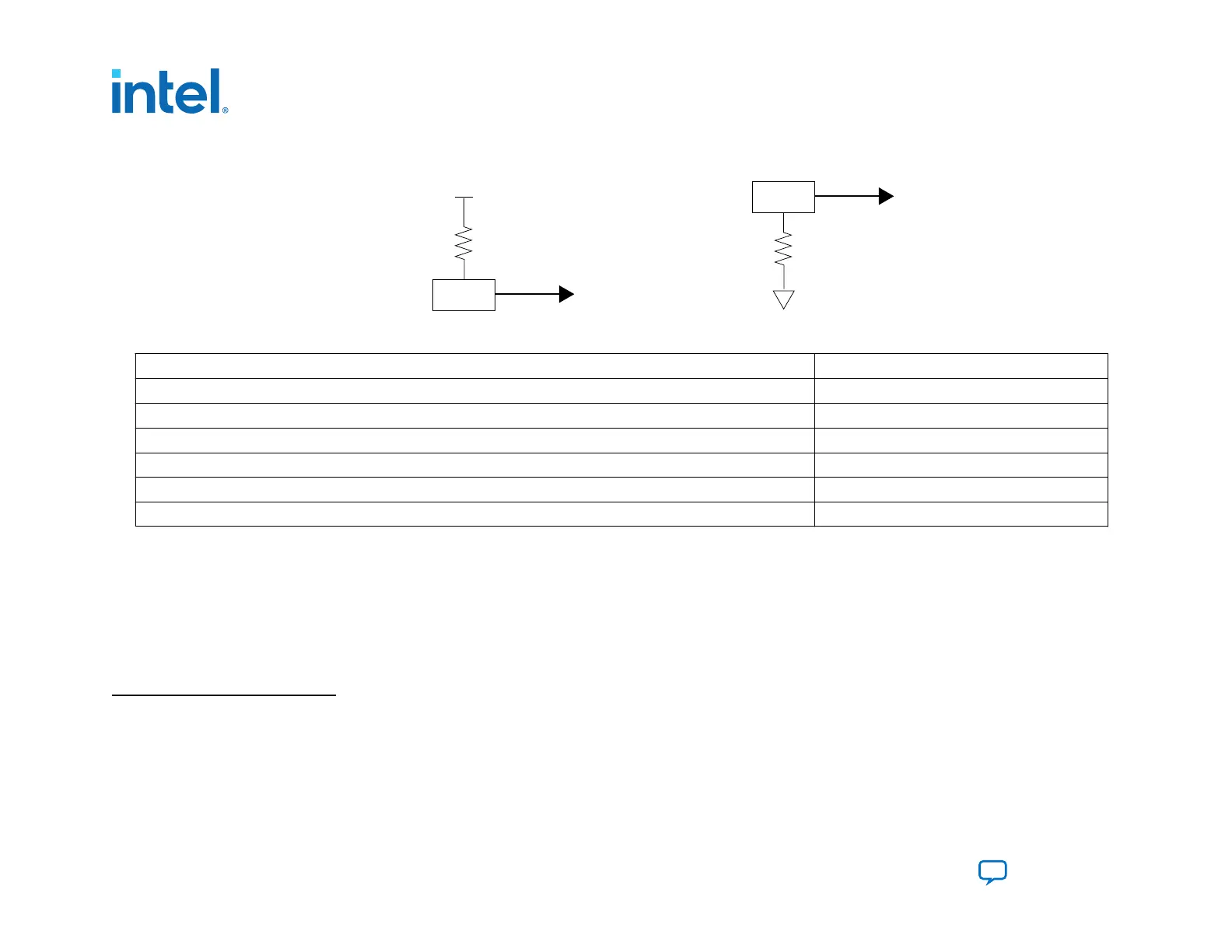

Table 5. MSEL Settings for Each Configuration Scheme of Intel Agilex Devices

Configuration Scheme MSEL[2:0]

Avalon-ST (x32) 000

Avalon-ST (x16) 101

Avalon-ST (x8) 110

AS (Fast mode – for CvP)

(5)

001

AS (Normal mode)

(6)

011

JTAG only

(7)

111

You must also specify the configuration scheme on the Configuration page of the Device and Pin Options dialog box in the

Intel Quartus Prime Software.

(5)

If you use AS Fast mode, you must ramp all power supplies to the recommended operating condition within 10 ms. This ramp-up

requirement ensures that the AS x4 device is within its operating voltage range when the Intel Agilex device begins to access it.

(6)

If you use AS Normal mode, you must fully ramp the V

CCIO_SDM

supply to the recommended operating condition within 10 ms.

(7)

JTAG configuration works with any valid MSEL settings, unless disabled for security.

2. Intel Agilex Configuration Details

683673 | 2021.10.29

Intel

®

Agilex

™

Configuration User Guide

Send Feedback

30

Loading...

Loading...