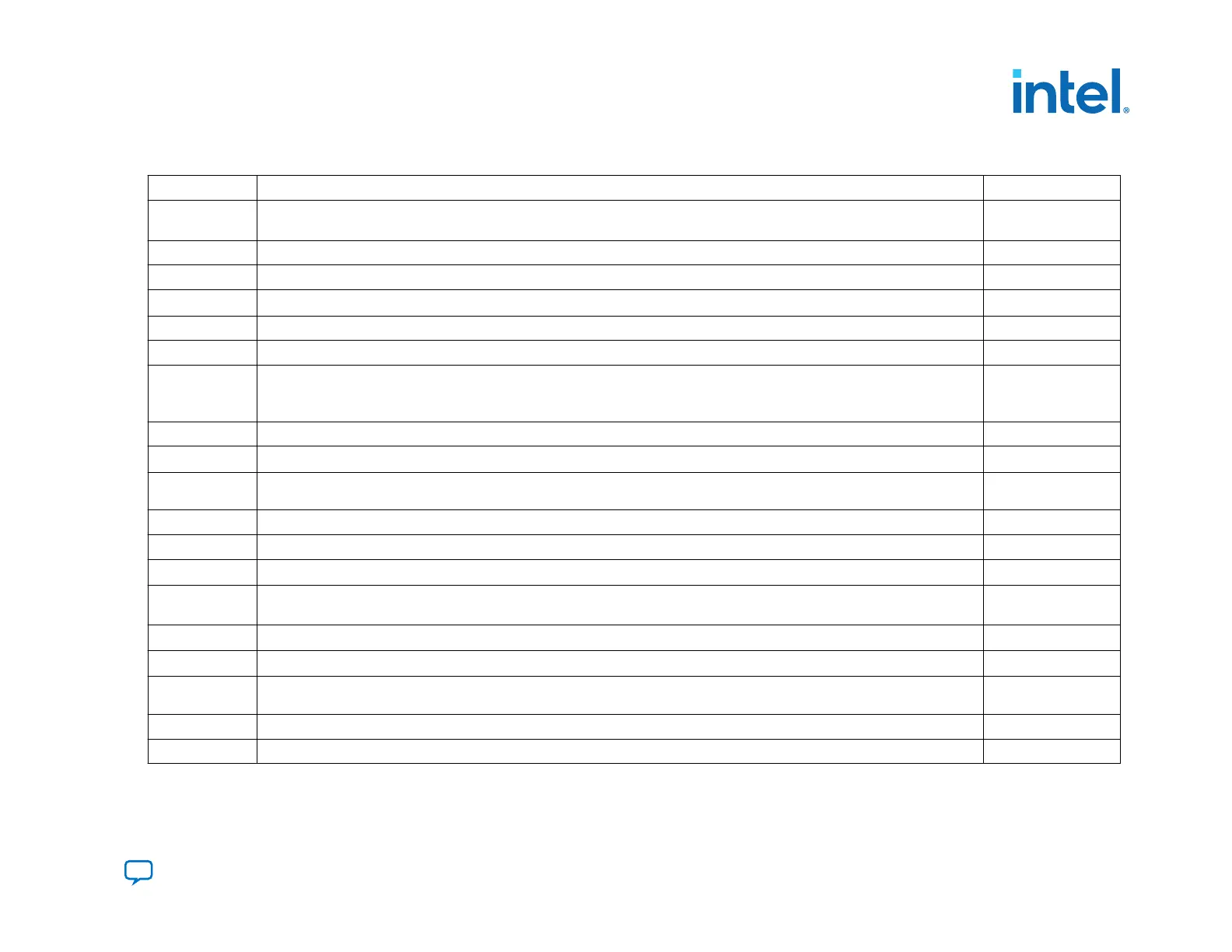

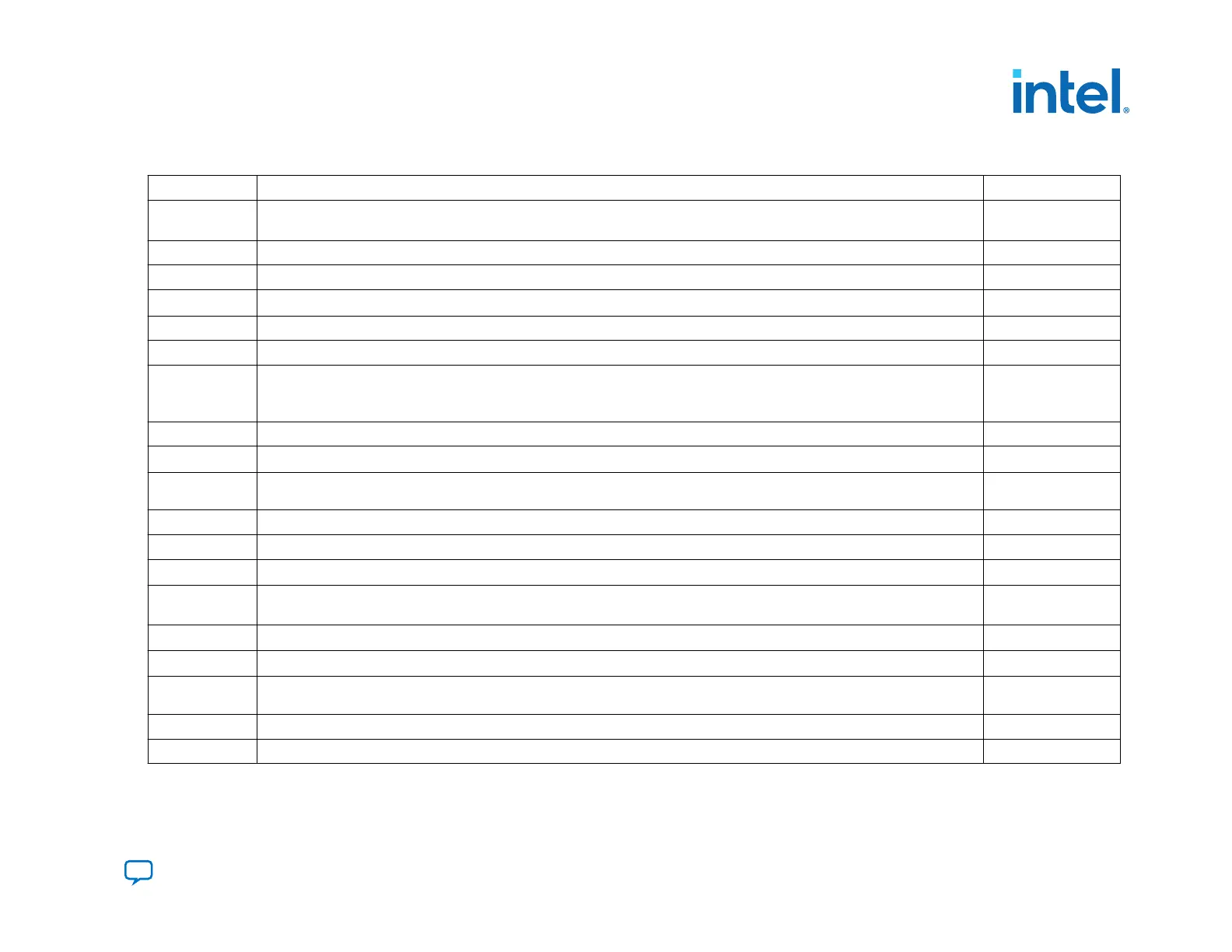

Table 53. General Configuration Debugging Checklist

Checklist Item Complete?

1

Verify that all configuration resistors are correctly connected (MSEL, nCONFIG, nSTATUS, CONF_DONE, INIT_DONE,

PWRMGT_SDA, PWRMGT_SCL).

☐

2 Verify that you are following the correct power-up and power-down sequences. ☐

3 Verify that the SDM I/Os assignments are correct by checking the Intel Quartus Prime Compilation QSF and Fitter reports. ☐

4

For SmartVID devices (-V or -E), ensure that all PMBus pins are connected to Intel Agilex device.

☐

5 Verify that SmartVID settings follow the recommendations in the Intel Agilex Power Management User Guide ☐

6 Verify that the Intel Agilex -V or -E device has its own voltage regulator module for V

CC

, V

CCP

, V

CCL_HPS

, and V

CCPLLDIG_HPS

☐

7

After configuration are the nCONFIG, nSTATUS, CONF_DONE, and INIT_DONE pins high?

For more information about configuration status, refer to the Understanding Configuration Status Using quartus_pgm Command

section.

☐

8 Is the SDM operating Boot ROM code or configuration firmware? ☐

9

Are the MSEL pins correctly connected on board?

☐

10 For designs that use transceivers, HBM2, PCIe, or EMIF, are the reference clocks stable and free running before configuration

begins?

☐

11 Verify that selected clocks match the frequency setting specified in the Intel Quartus Prime software during configuration. ☐

12 Does your design include the Reset Release IP? ☐

13

To avoid configuration failures, disconnect the PMBus regulator’s JTAG download cable before configuring Intel Agilex -V devices.

☐

14

Verify that the Intel Agilex device has exited POR by checking nCONFIG, nSTATUS, CONF_DONE and INIT_DONE pins using an

oscilloscope.

☐

15

Is the configuration clock source chosen appropriately? You can use an internal oscillator or the OSC_CLK_1 pin.

☐

16

For designs driving the OSC_CLK_1 pin is the frequency 25, 100, or 125 MHz?

☐

17 For Intel Agilex SX parts ensure that the HPS and EMIF IOPLL reference clocks are stable and free running before configuration

begins. The actual frequency should match the setting specified in Platform Designer.

☐

18 Are proper slave addresses set for the PMBus voltage regulator modules using the Intel Quartus Prime Software? ☐

19 For designs that use 3 V I/0, verify that the transceiver tiles are powered up before configuration begins. ☐

7. Intel Agilex Debugging Guide

683673 | 2021.10.29

Send Feedback

Intel

®

Agilex

™

Configuration User Guide

211

Loading...

Loading...