Configuration CP3003-SA

Page 4 - 14 ID 1052-6929, Rev. 3.0

D R A F T — F O R I N T E R N A L U S E O N L Y

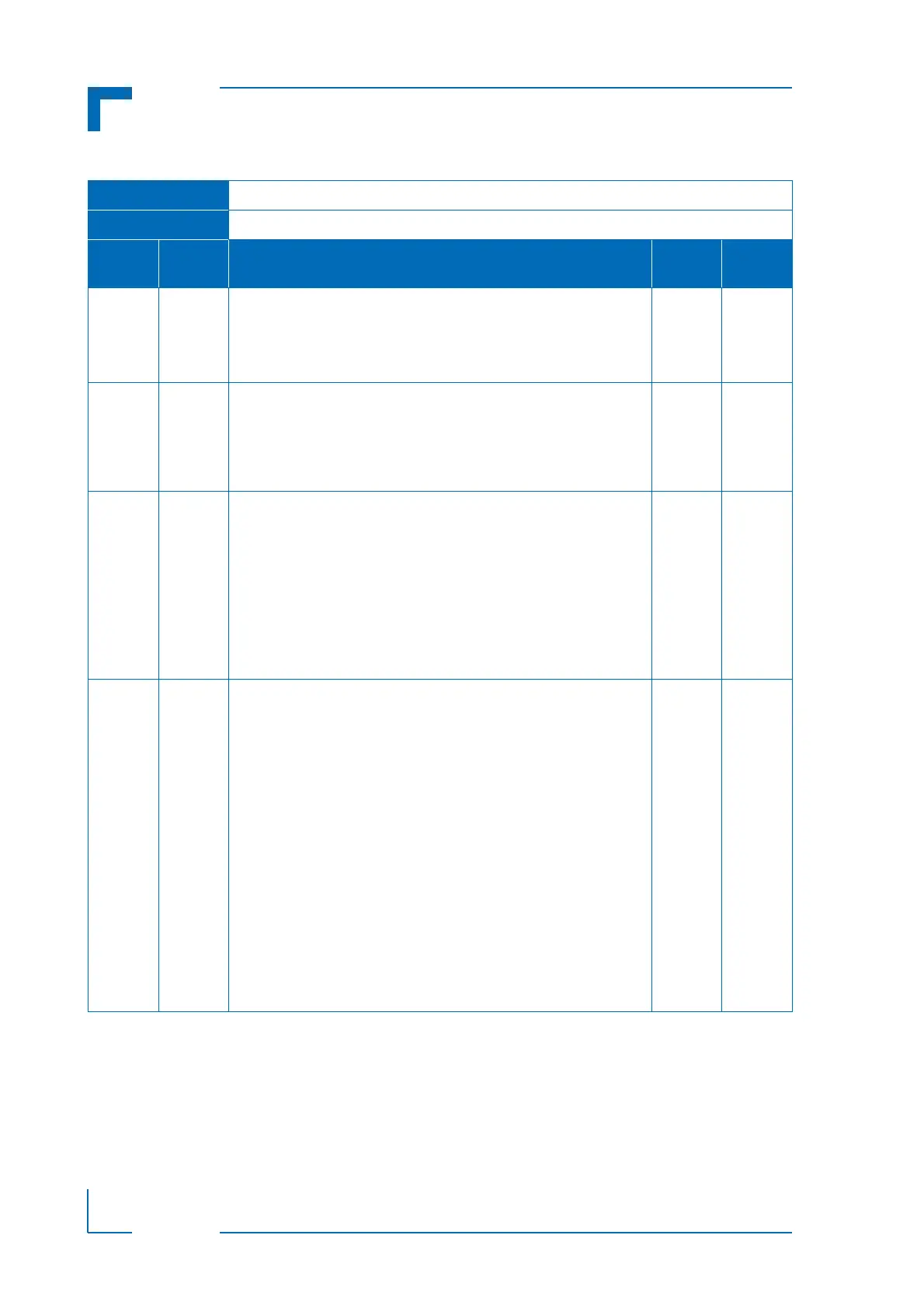

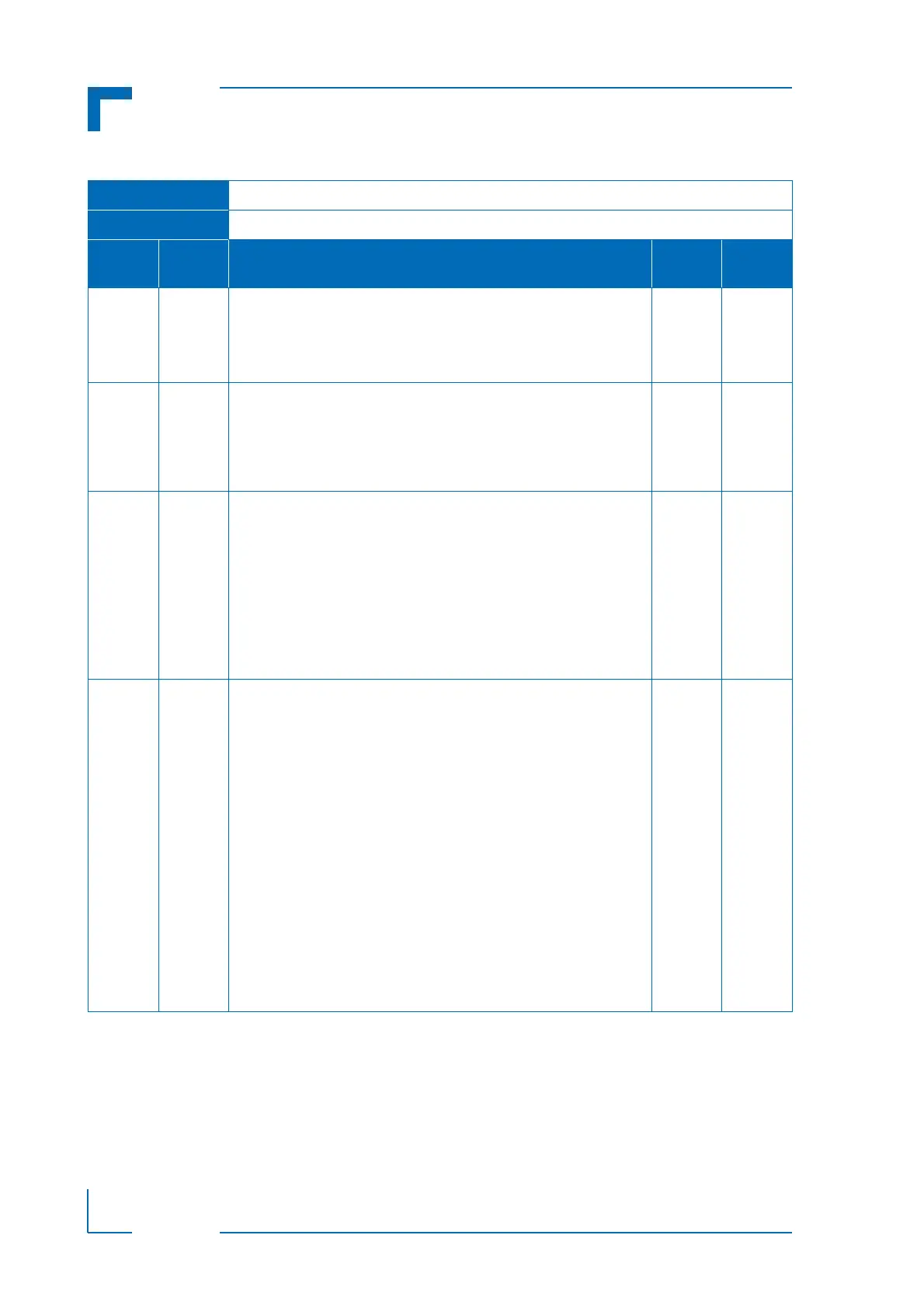

Table 4-15: Watchdog Timer Control Register (WTIM)

REGISTER NAME WATCHDOG TIMER CONTROL REGISTER (WTIM)

ADDRESS 0x28C

BIT NAME DESCRIPTION

RESET

VALUE

ACCESS

7 WTE Watchdog timer expired status bit

0 = Watchdog timer has not expired

1 = Watchdog timer has expired.

Writing a ’1’ to this bit resets it to 0.

0R/W

6 - 5 WMD Watchdog mode

00 = Timer only mode

01 = Reset mode

10 = Interrupt mode

11 = Cascaded mode (dual-stage mode)

00 R/W

4 WEN/WTR Watchdog enable/ Watchdog trigger control bit:

0 = Watchdog timer not enabled

Prior to the Watchdog being enabled, this bit is known as WEN.

After the Watchdog is enabled, it is known as WTR. Once the

Watchdog timer has been enabled, this bit cannot be reset to 0.

As long as the Watchdog timer is enabled, it will indicate a ’1’.

1 = Watchdog timer enabled

Writing a ’1’ to this bit causes the Watchdog to be retriggered to

the timer value indicated by bits WTM[3:0].

0R/W

3 - 0 WTM Watchdog timeout settings:

0000 = 0.125 s

0001 = 0.25 s

0010 = 0.5 s

0011 = 1 s

0100 = 2 s

0101 = 4 s

0110 = 8 s

0111 = 16 s

1000 = 32 s

1001 = 64 s

1010 = 128 s

1011 = 256 s

1100 = 512 s

1101 = 1024 s

1110 = 2048 s

1111 = 4096 s

0000 R/W

Loading...

Loading...