CP3003-SA Configuration

ID 1052-6929, Rev. 3.0 Page 4 - 5

D R A F T — F O R I N T E R N A L U S E O N L Y

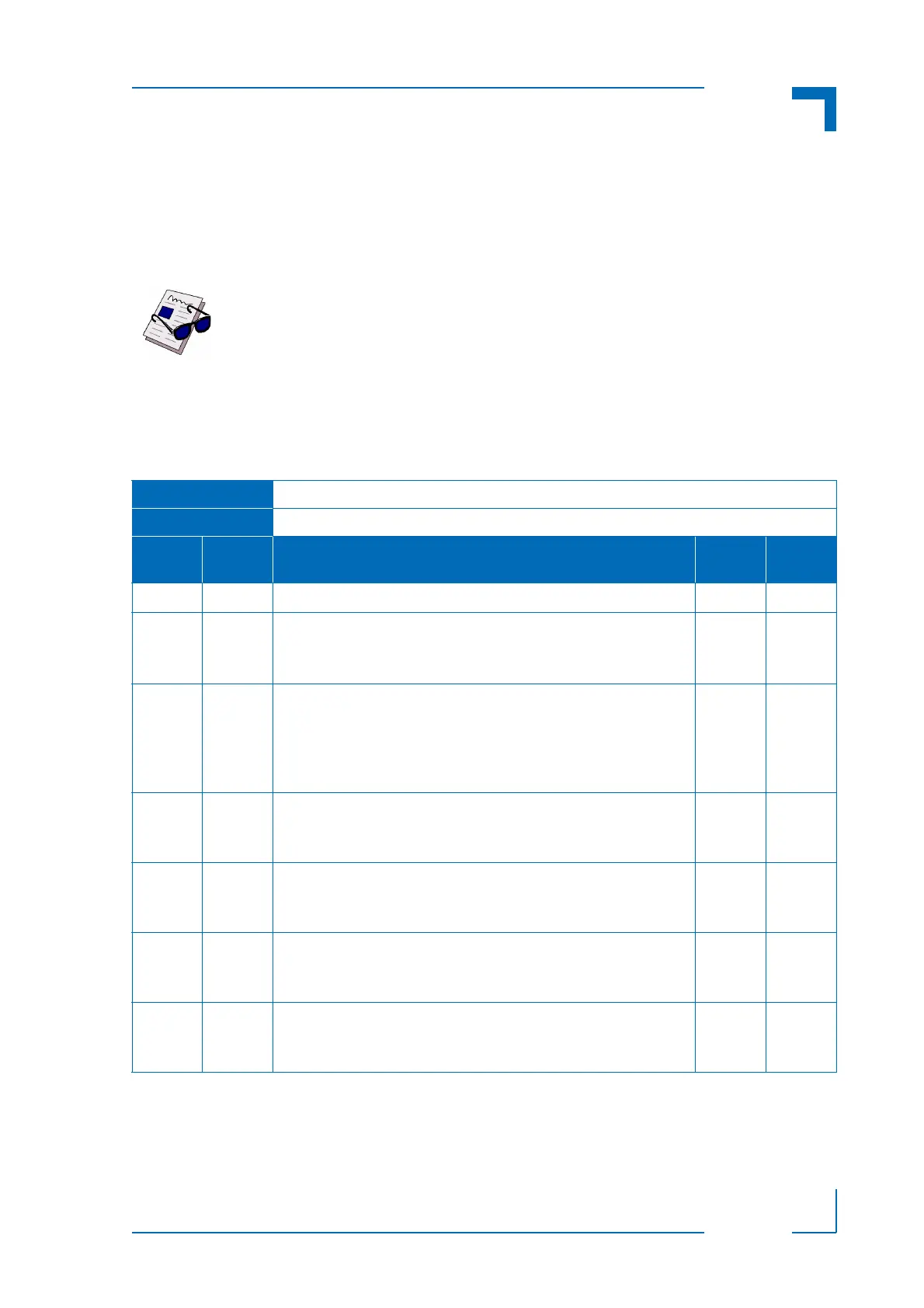

4.2 CP3003-SA-Specific Registers

The following registers are special registers which the CP3003-SA uses to watch the onboard

hardware special features and a number of CompactPCI control signals.

Normally, only the system uEFI BIOS uses these registers, but they are documented here for

application use as required.

4.2.1 Status Register 0 (STAT0)

The Status Register 0 holds general/common status information.

Note ...

Take care when modifying the contents of these registers as the system uEFI

BIOS may be relying on the state of the bits under its control.

Table 4-3: Status Register 0 (STAT0)

REGISTER NAME STATUS REGISTER 0 (STAT0)

ADDRESS 0x280

BIT NAME DESCRIPTION

RESET

VALUE

ACCESS

7 Res. Reserved 0 R

6 BBEI uEFI BIOS boot end indication:

0 = uEFI BIOS is booting

1 = uEFI BIOS boot is finished

0R

5 - 4 BFSS SPI boot flash selection status:

00 = Standard SPI boot flash active

01 = Recovery SPI boot flash active

10 = External SPI boot flash active

11 = Reserved

N/A R

3 DIP4 DIP switch SW1, switch 4 (clear the uEFI BIOS settings):

0 = Switch on (boot using the currently saved uEFI BIOS settings)

1 = Switch off (clear the uEFI BIOS settings)

N/A R

2 DIP3 DIP switch SW1, switch 3 (reset configuration):

0 = Switch on (level-sensitive reset configuration)

1 = Switch off (edge-sensitive reset configuration)

N/A R

1 DIP1 DIP switch SW1, switch 2 (select SPI flash):

0 = Switch on (boot from standard SPI boot flash)

1 = Switch off (boot from recovery SPI boot flash)

N/A R

0 DIP0 DIP switch SW1, switch 1 (POST code indication on LED0..3):

0 = Switch on (boot-up with POST code indication on LED0..3)

1 = Switch off (boot-up with no POST code indication on LED0..3)

N/A R

Loading...

Loading...