Doc. No. MV-S104859-U0 Rev. E Copyright © 2008 Marvell

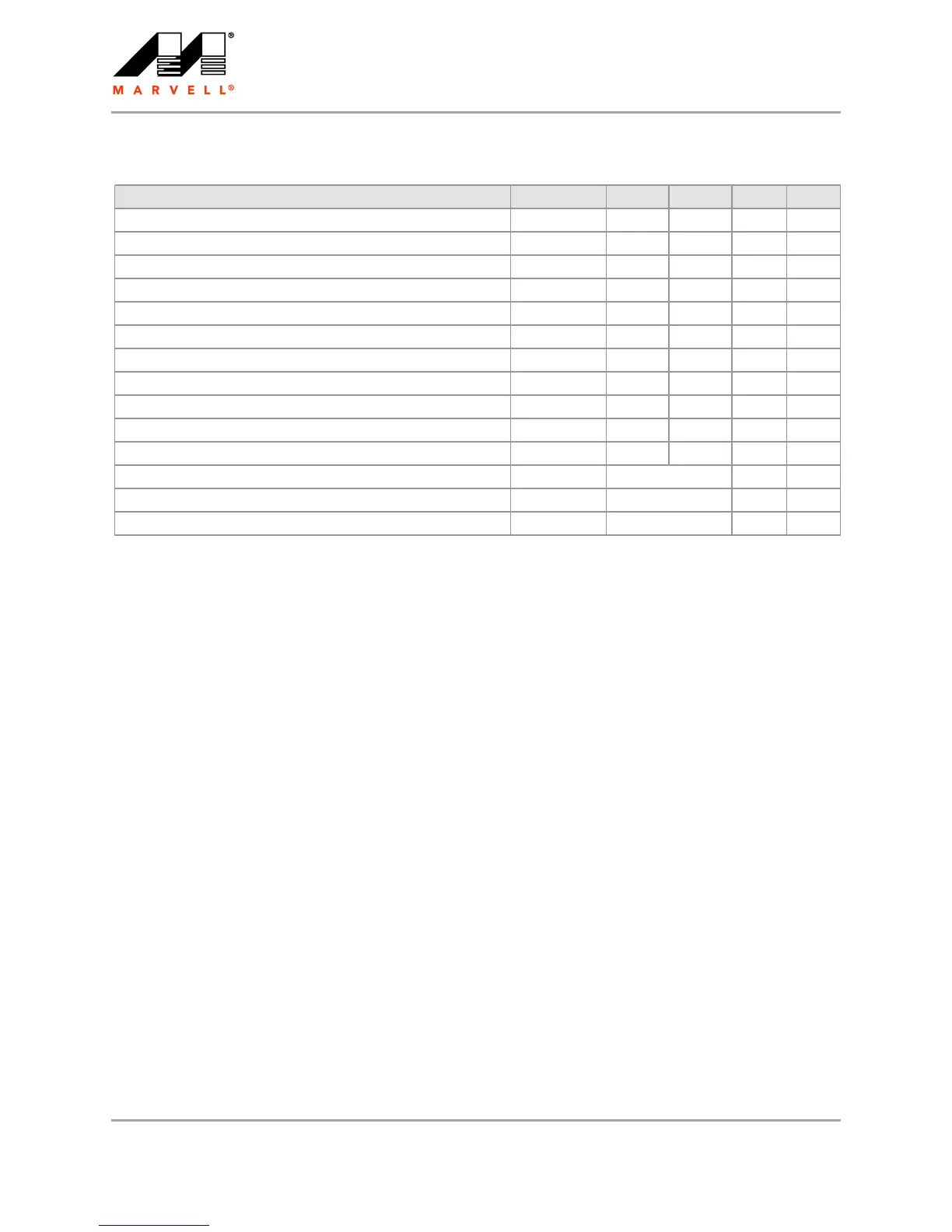

Description Symbol Min Max Units Notes

Clock period jitter tJIT(per) -100 100 ps 1

Clock perior jitter during DLL locking period tJIT(per,lck) -80 80 ps 2

Cycle to cycle clock period jitter tJIT(cc) -200 200 ps 3

Cycle to cycle clock period jitter during DLL locking period tJIT(cc,lck) -160 160 ps 4

Cumulative error across 2 cycles tERR(2per) -150 150 ps 5

Cumulative error across 3 cycles tERR(3per) -175 175 ps 5

Cumulative error across 4 cycles tERR(4per) -200 200 ps 5

Cumulative error across 5 cycles tERR(5per) -200 200 ps 5

Cumulative error across n cycles, n=6...10, inclusive tERR(6-10per) -300 300 ps 5

Cumulative error across n cycles, n=11…50, inclusive tERR(11-50per) -450 450 ps 5

Duty cycle jitter tJIT(duty) -100 100 ps 6

Absolute clock period tCK(abs) ps 7

Absolute clock high pulse w idth tCH(abs) ps 8

Absolute clock low pulse w idth tCL(abs) ps 9

Note s:

General comment: All timing values are defined on CLK / CLKn crossing point, unless otherw ise specified.

1. tJIT(per) is defined as the largest deviation of any single tCK from tCK(avg).

tJIT(per) = Min/max of {tCKi- tCK(avg) w here i=1 to 200}.

tJIT(per) defines the single period jitter w hen the DLL is already locked.

2. tJIT(per,lck) uses the same definition for single period jitter, during the DLL locking period only.

3. tJIT(cc) is defined as the difference in clock period between tw o consecutive clock cycles: tJIT(cc) = Max of |tCKi+1 – tCKi|.

tJIT(cc) defines the cycle to cycle jitter when the DLL is already locked.

4. tJIT(cc,lck) uses the same definition for cycle to cycle jitter, during the DLL locking period only.

5. tERR is defined as the cumulative error across multiple consecutive cycles from tCK(avg).

Please refer to JEDEC Standard No. 79-2C (DDR2 SDRAM Specification), Chapter 5 (page 100) for more information.

6. tJIT(duty) is defined as the cumulative set of tCH jitter and tCL jitter. tCH jitter is the largest deviation of

any single tCH from tCH(avg). tCL jitter is the largest deviation of any single tCL from tCL(avg).

tJIT(duty) = Min/max of {tJIT(CH), tJIT(CL)} w here,

tJIT(CH) = {tCHi- tCH(avg) w here i=1 to 200}; tJIT(CL) = {tCLi- tCL(avg) w here i=1 to 200}.

7. tCK(abs),min = tCK(avg),min + tJIT(per),min; tCK(abs),max = tCK(avg),max + tJIT(per),max.

8. tCH(abs),min = tCH(avg),min x tCK(avg),min + tJIT(duty),min; tCH(abs),max = tCH(avg),max x tCK(avg),max + tJIT(duty),max.

9. tCL(abs),min = tCL(avg),min x tCK(avg),min + tJIT(duty),min; tCL(abs),max = tCL(avg),max x tCK(avg),max + tJIT(duty),max.

See note 7

See note 8

See note 9

Loading...

Loading...