Clocking

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 61

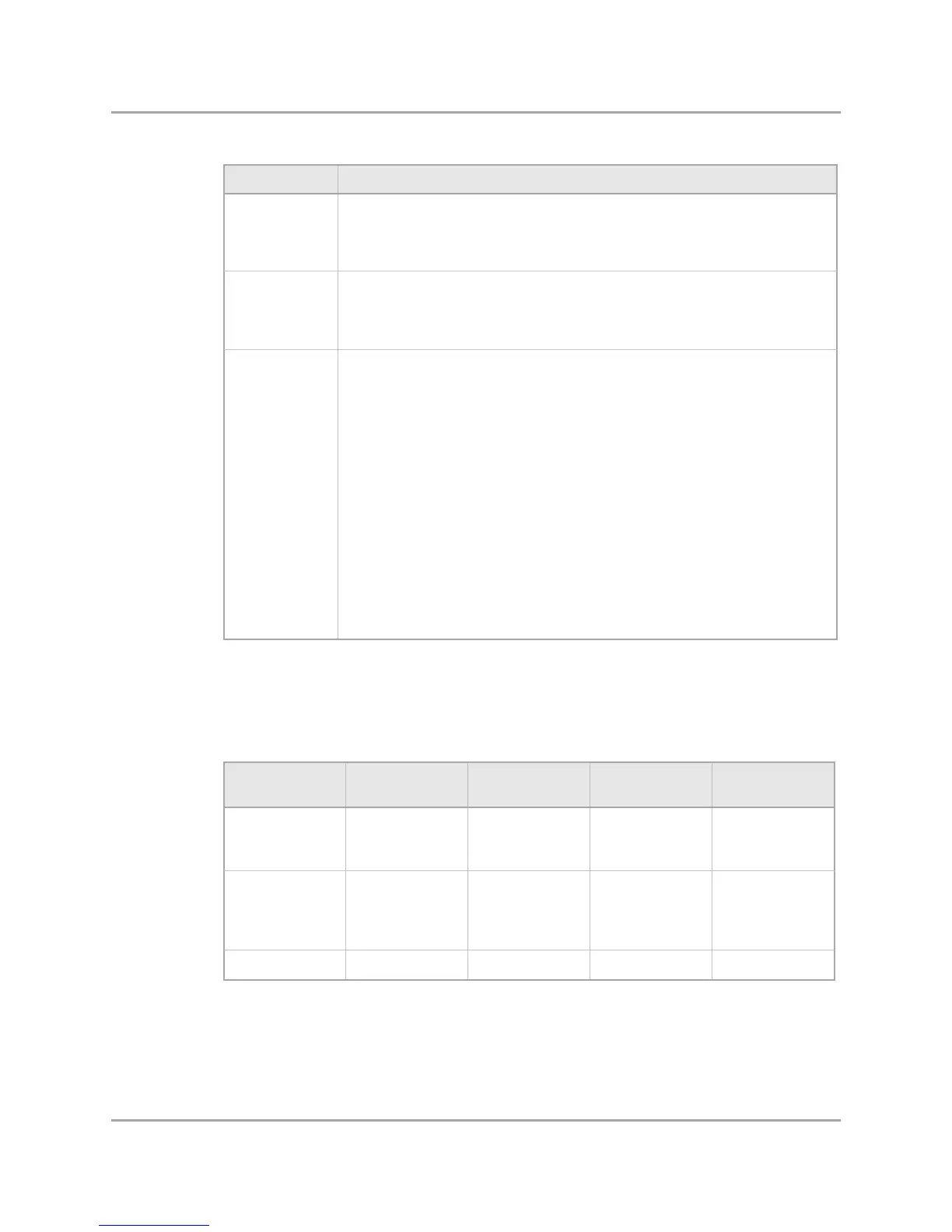

The following table lists the supported combinations of the CPU_CLK Frequency select, CPU_CLK

to DDR CLK ratio, and to CPU_CLK to CPU L2 clock ratio (see Section 6.5, Pins Sample

Configuration, on page 66).

SATA PHY PLL

• Reference clock:

REF_CLK_XIN (25 MHz)

• Derivative clock:

SATA Clock (150 MHz)

RTC

• Reference clock:

RTC_XIN (32.768 kHz)

Used for real time clock functionality, see the Real Time Clock section in the

88F6180, 88F6190, 88F6192, and 88F6281 Functional Specifications.

PTP

• Reference clock:

PTP_CLK (125 MHz)

The PTP_CLK can be used for the following functions:

• PTP time stamp clock

Two options for reference clock:

- PTP_CLK

- Gigabit Ethernet Clock (125 MHz)

• TS unit clock

Two options for reference clock:

- PTP_CLK/2

- Core PLL

• Audio unit clock

Two options for reference clock:

- PTP_CLK

- REF_CLK_XIN (25 MHz)

For clocking configuration registers, see the 88F6180, 88F6190, 88F6192, and

88F6281 Functional Specifications.

Table 30: Supported Clock Combinations

DDR Clock

(MHz)

CPU to DDR

Clock Ratio

CPU Clock

(MHz)

CPU to L2

Clock Ratio

L2 Clock

(MHz)

333

250

200

3:1

4:1

5:1

1000 3:1 333

400

300

267

200

3:1

4:1

4.5:1

6:1

1200 3:1 400

375 4:1 1500 3:1 500

Table 29: 88F6281Clocks (Continued)

Clock Type Description

Loading...

Loading...