Pin Multiplexing

Gigabit Ethernet (GbE) Pins Multiplexing on MPP

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 57

4.2 Gigabit Ethernet (GbE) Pins Multiplexing on MPP

The 88F6281 has 14 dedicated pins for its GbE port. (12 RGMII pins, an MDC pin, and an MDIO

pin).

For the 88F6281, additional GbE interface pins are multiplexed on the MPPs, to serve as the

following interfaces to an external PHY or switch.

Two RGMII ports

One RGMII port and one MMII/MII port

(either port 0 as RGMII and port 1 as MMII/MII or port 0 as MMII/MII and port 1 as RGMII)

One GMII port (port 0)

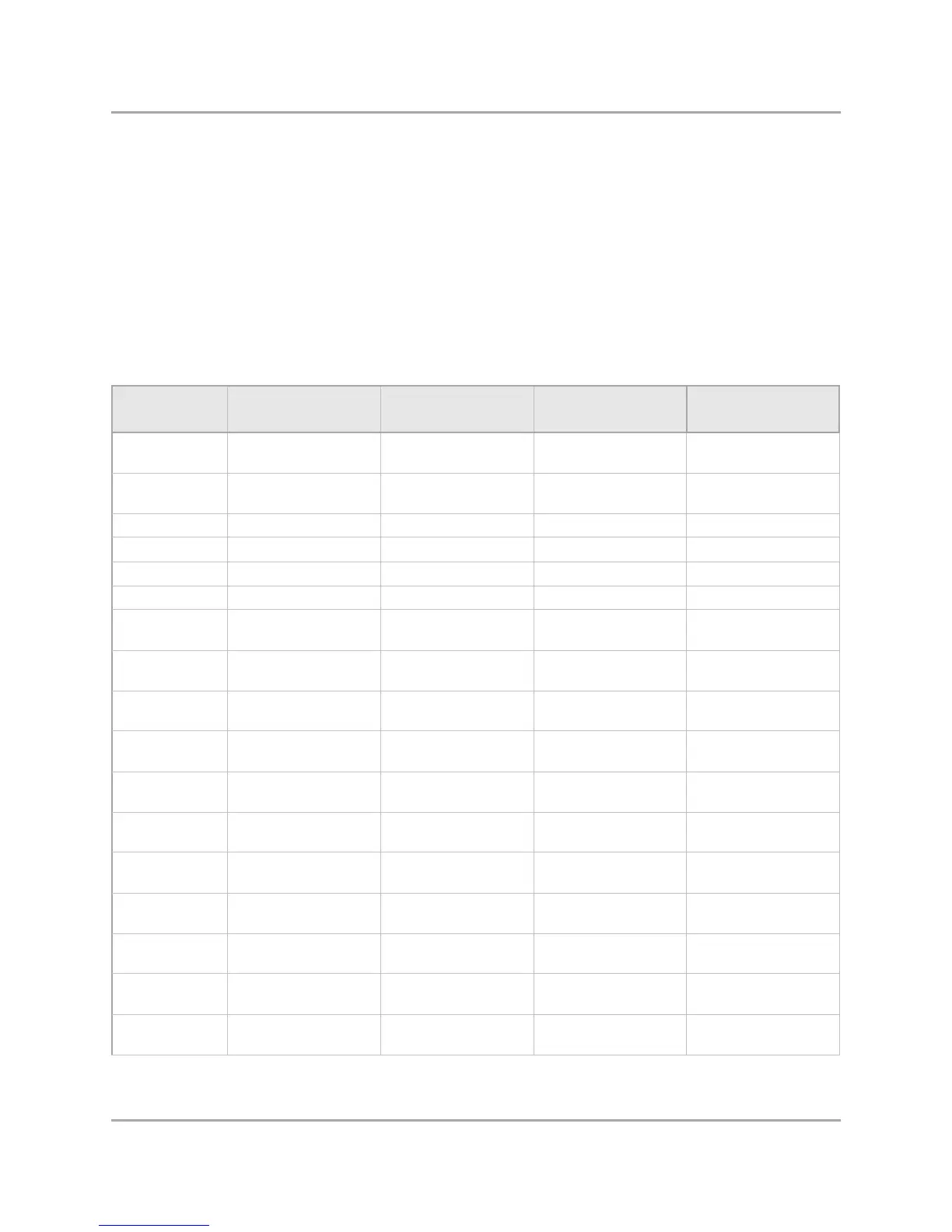

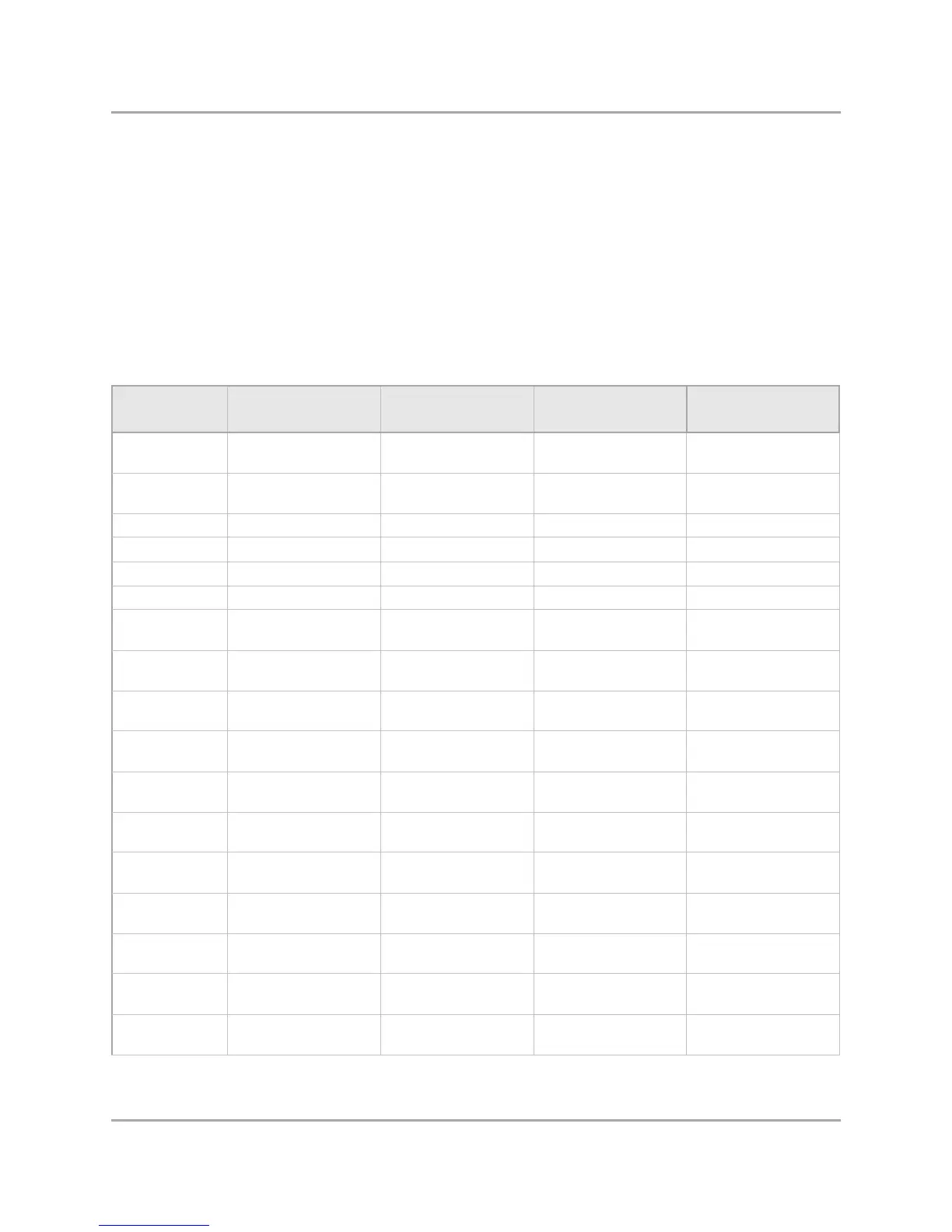

Table 27 summarizes the GbE port pins multiplexing.

Table 27: Ethernet Ports Pins Multiplexing

Pin Name 1xGMII RGMII0+MII1/

MMII1

2xRGMII MII0/MMII0+

RGMII1

GE_TXCLKOUT GMII0_TXCLKOUT

(out)

RGMII0_TXCLKOUT

(out)

RGMII0_TXCLKOUT

(out)

MII0_TXCLK (in)

GE_TXD[3:0] GMII0_TXD[3:0] (out) RGMII0_TXD[3:0]

(out)

RGMII0_TXD[3:0]

(out)

MII0_TXD[3:0] (out)

GE_TXCTL GMII0_TXEN (out) RGMII0_TXCTL (out) RGMII0_TXCTL (out) MII0_TXEN (out)

GE_RXD[3:0] GMII0_RXD[3:0] (in) RGMII0_RXD[3:0] (in) RGMII0_RXD[3:0] (in) MII0_RXD[3:0] (in)

GE_RXCTL GMII0_RXDV (in) RGMII0_RXCTL (in) RGMII0_RXCTL (in) MII0_RXDV (in)

GE_RXCLK GMII0_RXCLK (in) RGMII0_RXCLK (in) RGMII0_RXCLK (in) MII0_RXCLK (in)

MPP[8] or

MPP[35]

NA NA NA MII0_RXERR (in)

MPP[8] or

MPP[14]

NA NA NA MII0_COL (in)

MPP[9] or

MPP[16]

NA NA NA MII0_CRS (in)

MPP [23:20] /

GE1[3:0]

GMII0_TXD[7:4] (out) MII1_TXD[3:0] (out) RGMII1_TXD[3:0]

(out)

RGMII1_TXD[3:0]

(out)

MPP_[27:24] /

GE1[7:4]

GMII0_RXD[7:4] (in) MII1_RXD[3:0] (in) RGMII1_RXD[3:0] (in) RGMII1_RXD[3:0] (in)

MPP_28 /

GE1[8]

GMII0_COL (in) MII1_COL (in) NA NA

MPP_29 /

GE1[9]

GMII0_TXCLK (in) MII1_TXCLK (in) NA NA

MPP_30 /

GE1[10]

GMII0_RXERR (in) MII1_RXDV (in) RGMII1_RXCTL (in) RGMII1_RXCTL (in)

MPP_31 /

GE1[11]

NA MII1_RXCLK (in) RGMII1_RXCLK (in) RGMII1_RXCLK (in)

MPP_32 /

GE1[12]

GMII0_CRS (in) MII1_CRS (in) RGMII1_TXCLKOUT

(out)

RGMII1_TXCLKOUT

(out)

MPP_33 /

GE1[13]

GMII0_TXERR (out) MII1_TXERR (out) RGMII1_TXCTL (out) RGMII1_TXCTL (out)

Loading...

Loading...