Electrical Specifications

DC Electrical Specifications

Copyright © 2008 Marvell Doc. No. MV-S104859-U0 Rev. E

December 2, 2008, Preliminary Document Classification: Proprietary Information Page 81

8.5 DC Electrical Specifications

8.5.1 General 3.3V (CMOS) DC Electrical Specifications

The DC electrical specifications in Table 39 are applicable for the following interfaces and signals:

JTAG

RGMII (10/100 Mbps)/GMII/MII/MMII

Secure Digital Input/Output (SDIO)

S/PDIF / I

2

S (Audio)

Transport Stream (TS)

NAND flash

UART

MPP

PTP

SYSRSTn

In the following table, for the JTAG, SDIO, S/PDIF / I

2

S, TS, NAND flash, UART, PTP, and MPP

interfaces, VDDIO means the VDDO power rail. For the RGMII/GMII/MII/MMII interface, VDDIO

means the VDD_GE_A and VDD_GE_B power rails.

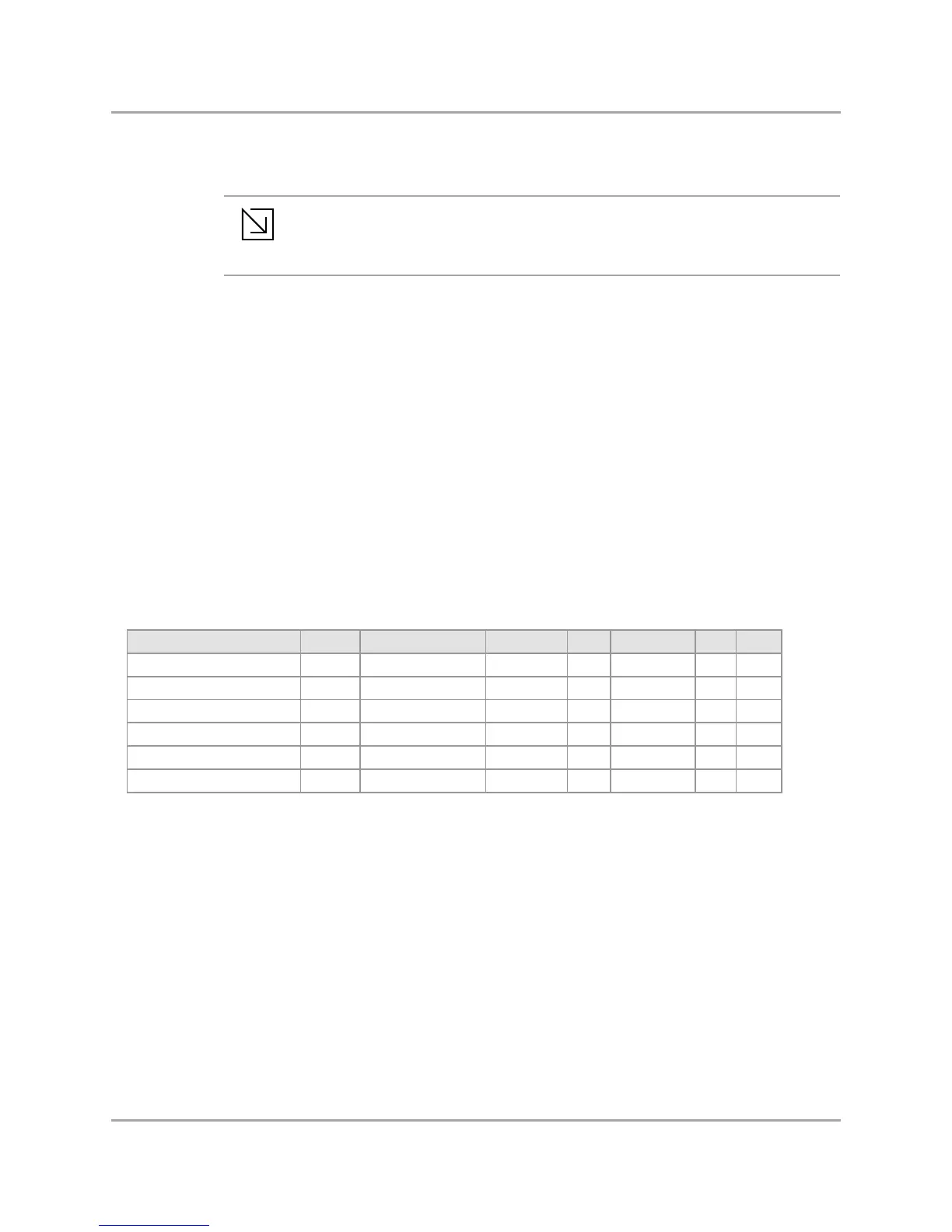

Table 39: General 3.3V Interface (CMOS) DC Electrical Specifications

See Section 1.3, Internal Pull-up and Pull-down Pins, on page 48 for internal

pullup/pulldown information.

Parameter Symbol Test Condition Min Typ Max Units Notes

Input low level VIL -0.3 0.8 V -

Input high level VIH 2.0 VDDIO+0.3 V -

Output low level VOL IOL = 2 mA - 0.4 V -

Output high level VOH IOH = -2 mA 2.4 - V -

Input leakage current IIL 0 < VIN < VDDIO -10 10 uA 1, 2

Pin capacitance Cpin 5 pF -

Note s:

General comment: See the Pin Description section for internal pullup/pulldow n.

1. While I/O is in High-Z.

2. This current does not include the current flow ing through the pullup/pulldow n resistor.

Loading...

Loading...