MS51

Nov. 28, 2019 Page 136 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

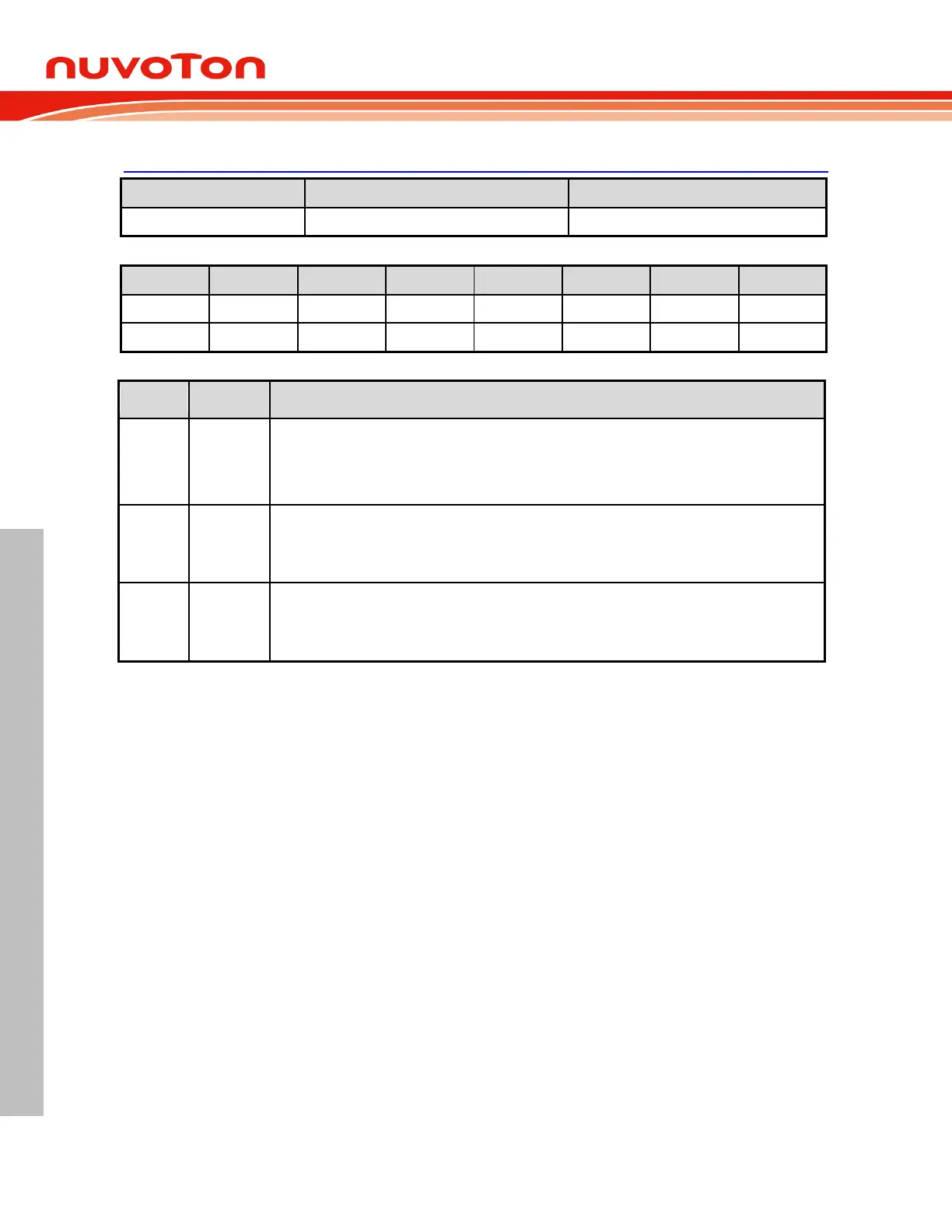

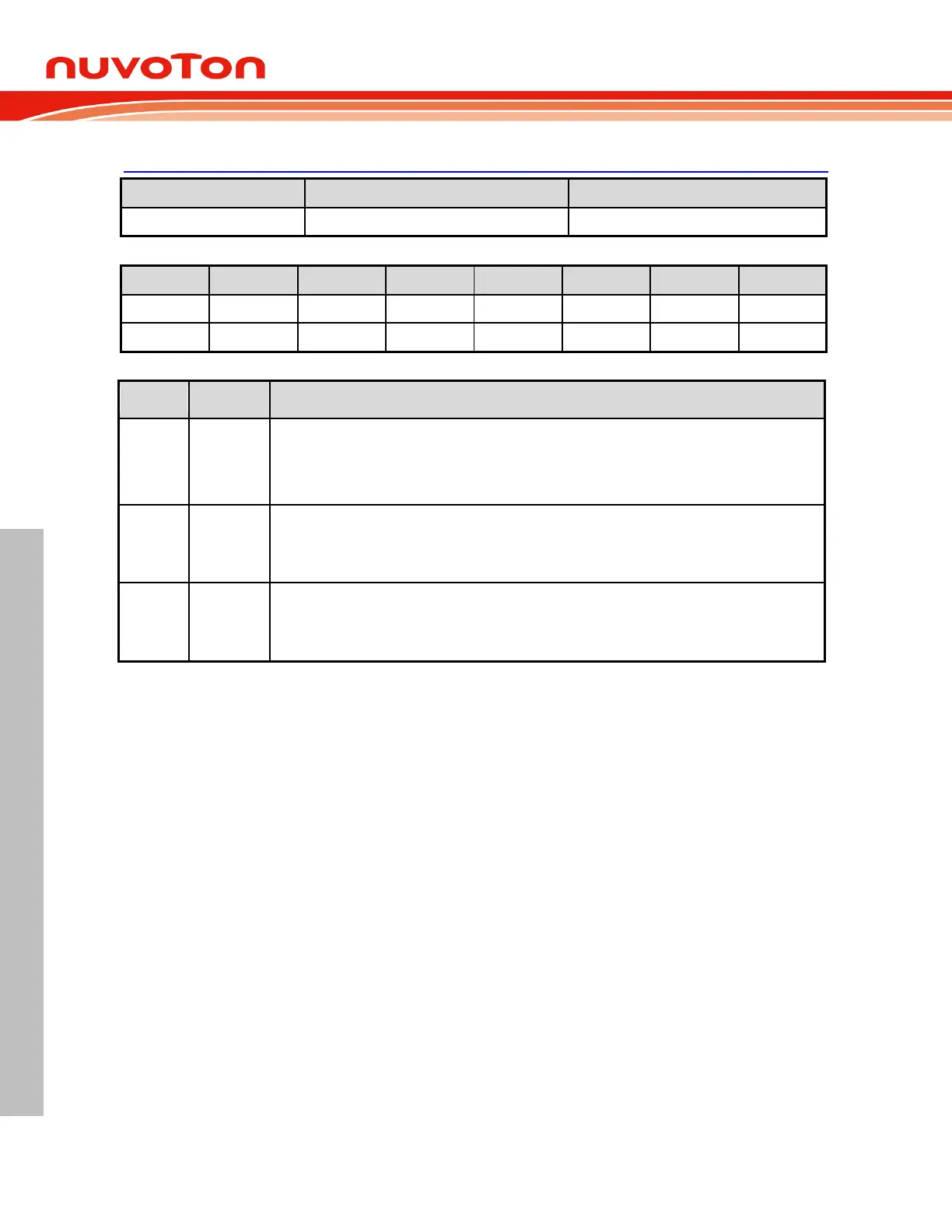

PWM0FBD – PWM Fault Brake Data

Fault Brake flag

This flag is set when FBINEN is set as 1 and FB pin detects an edge, which matches FBINLS

(PWM0FBD.6) selection. This bit is cleared by software. After FBF is cleared, Fault Brake data

output will not be released until PWM0RUN (PWM0CON0.7) is set.

PWM_BRAKE pin input level selection

0 = Falling edge.

1 = Rising edge.

PWMn Fault Brake data

0 = PWMn signal is overwritten by 0 once Fault Brake asserted.

1 = PWMn signal is overwritten by 1 once Fault Brake asserted.

Loading...

Loading...