MS51

Nov. 28, 2019 Page 438 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

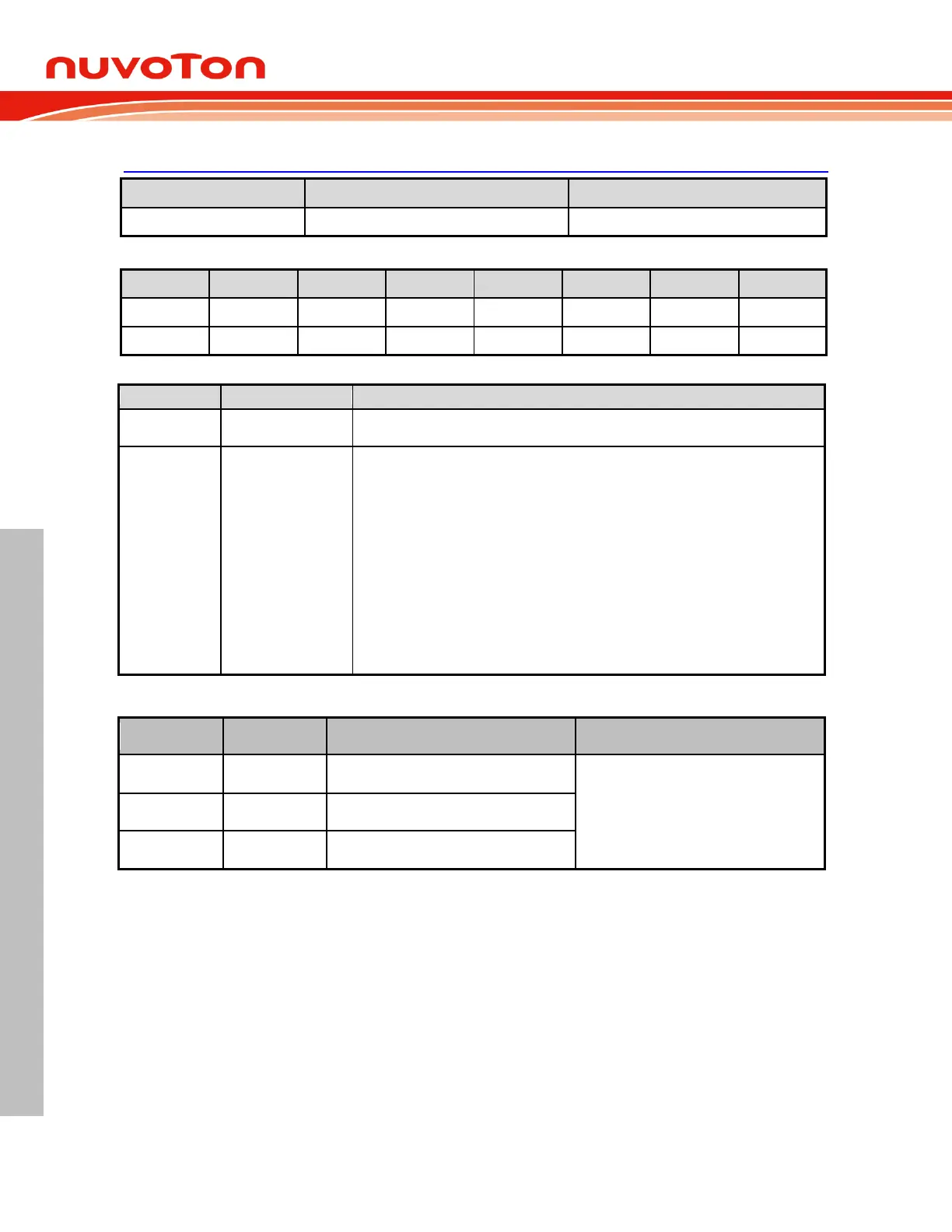

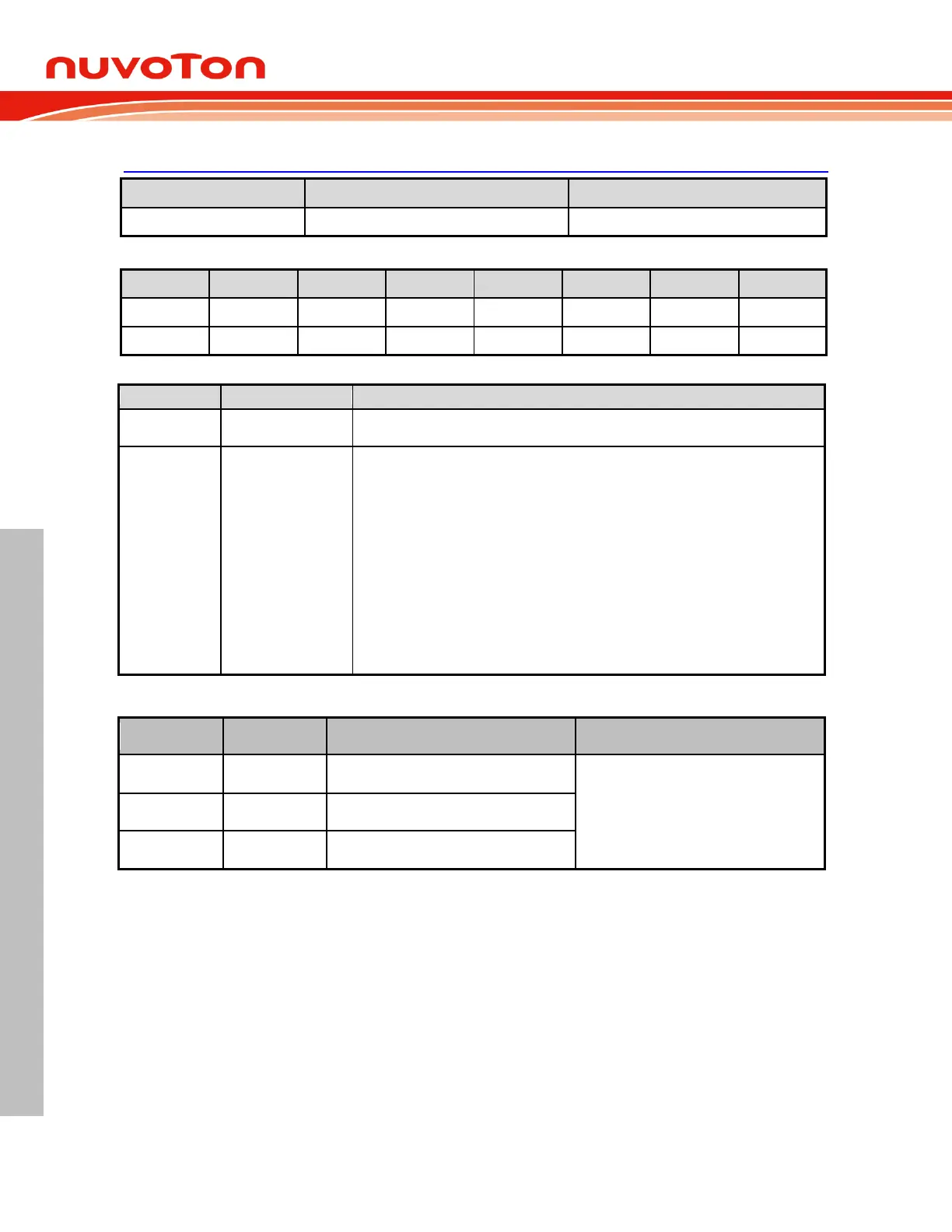

SPCR2 – Serial Peripheral Control Register 2

SPI Interval time selection between adjacent bytes

SPIS[1:0] and CPHA select eight grades of SPI interval time selection between

adjacent bytes. As below table:

SPIS[1:0] are valid only under Master mode (MSTR = 1).

Table 6.12-1 Slave Select Pin Configurations

Loading...

Loading...