MS51

Nov. 28, 2019 Page 433 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

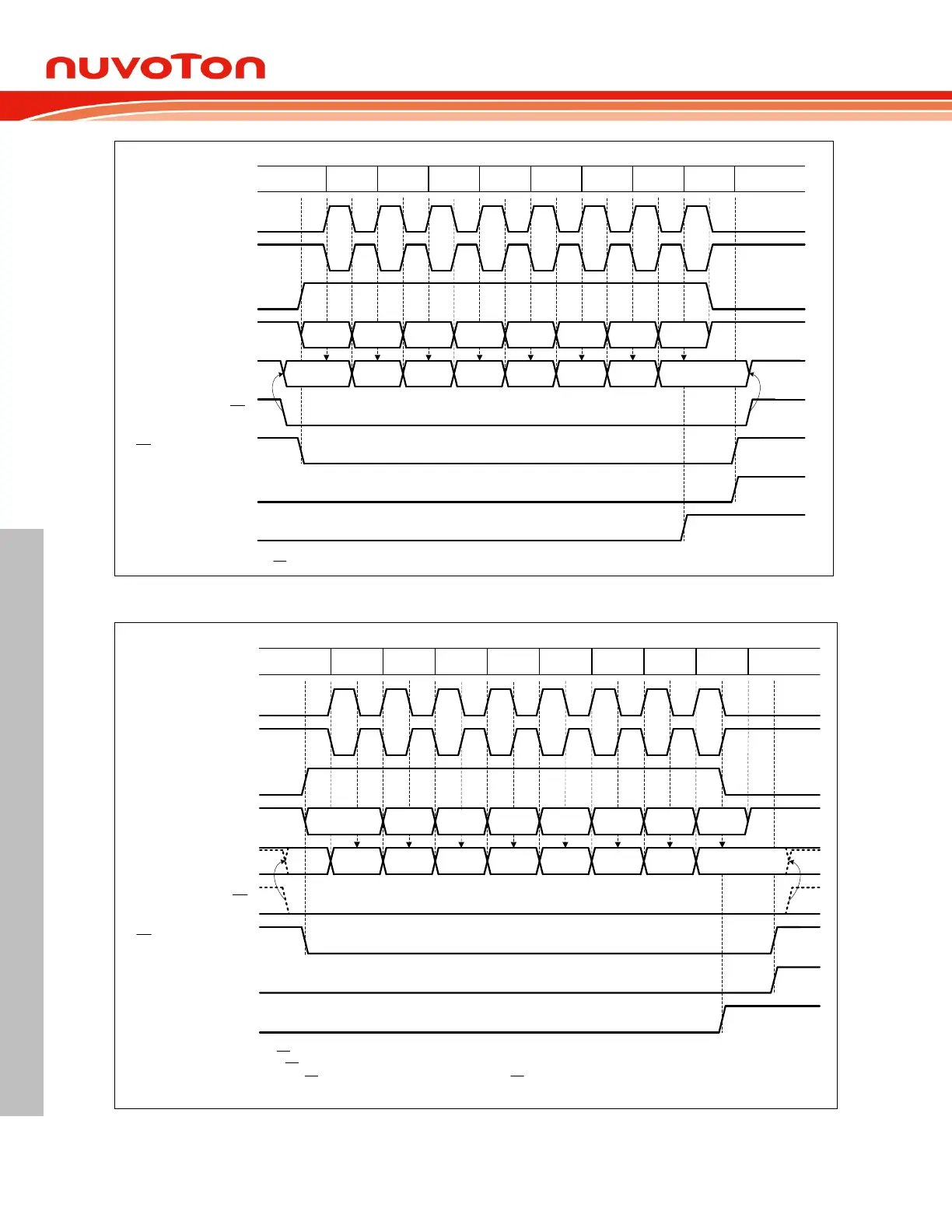

SPCLK Cycles

SPCLK (CPOL=0)

MOSI

SS output of Master

[2]

SPIF (Master)

1 2 3 4 5 6 7 8

SPCLK (CPOL=1)

Transfer Progress

[1]

(internal signal)

MSB

MISO

6

5

4

3

2 1

LSB

MSB

Input to Slave SS

LSB

6 5 4

3

2

1

SPIF (Slave)

[1] Transfer progress starts by a writing SPDR of Master MCU.

[2] SS automatic output affects when MSTR = DISMODF = SSOE = 1.

SPCLK Cycles

Figure 6.12-5 SPI Clock and Data Format with CPHA = 0

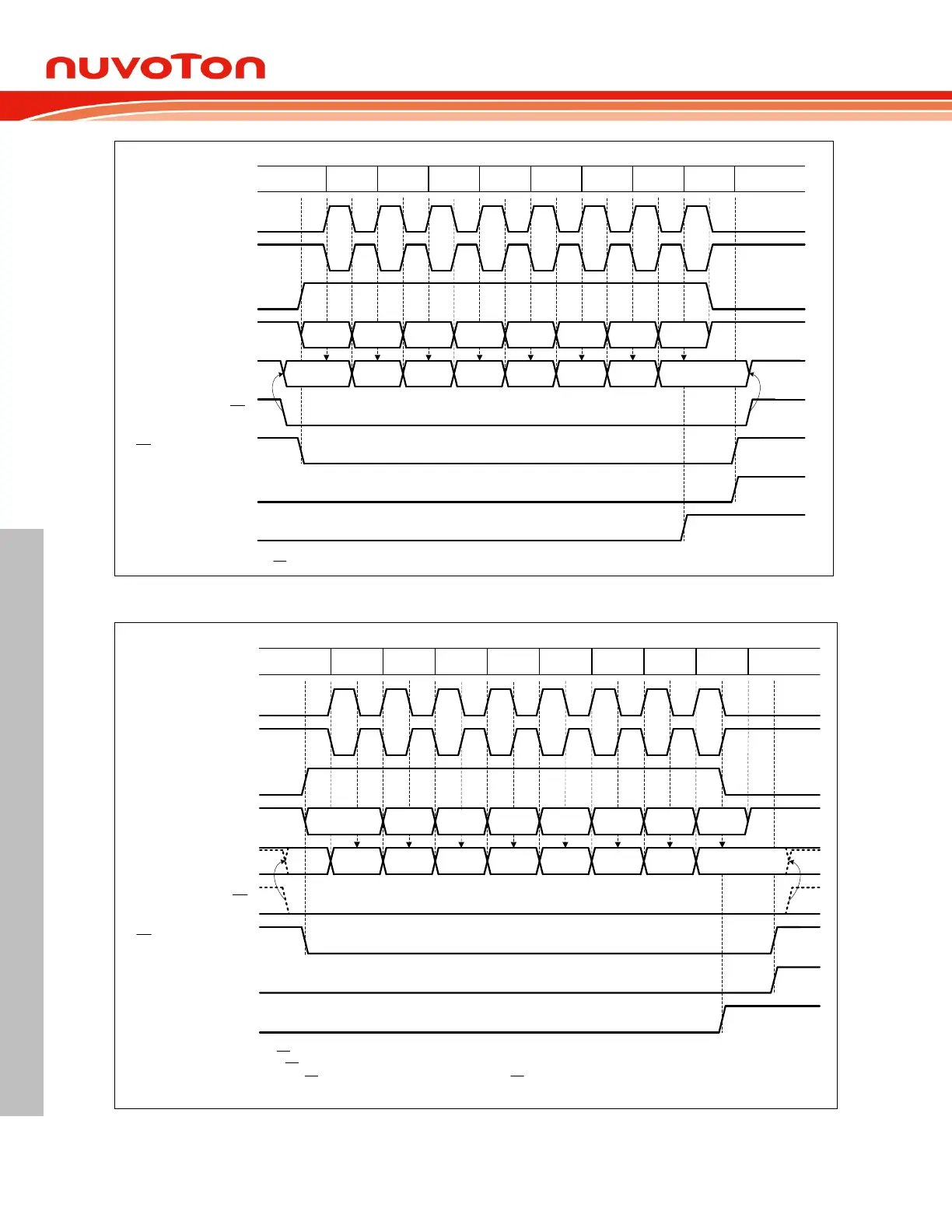

Transfer Progress

[1]

(internal signal)

SPCLK Cycles

SPCLK (CPOL=0)

MOSI

SS output of Master

[2]

SPIF (Master)

1 2 3 4 5 6 7 8

SPCLK (CPOL=1)

MSB

MISO

6

5

4

3

2 1

LSB

MSB

Input to Slave SS

LSB

6

5

4

3 2

1

SPIF (Slave)

[1] Transfer progress starts by a writing SPDR of Master MCU.

[2] SS automatic output affects when DISMODF = SSOE = MSTR = 1.

[3] If SS of Slave is low, the MISO will be the LSB of previous data. Otherwise, MISO will be high.

[4] While SS stays low, the LSB will last its state. Once SS is released to high, MISO will switch to high level.

[3] [4]

SPCLK Cycles

Figure 6.12-6 SPI Clock and Data Format with CPHA = 1

Loading...

Loading...