MS51

Nov. 28, 2019 Page 320 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

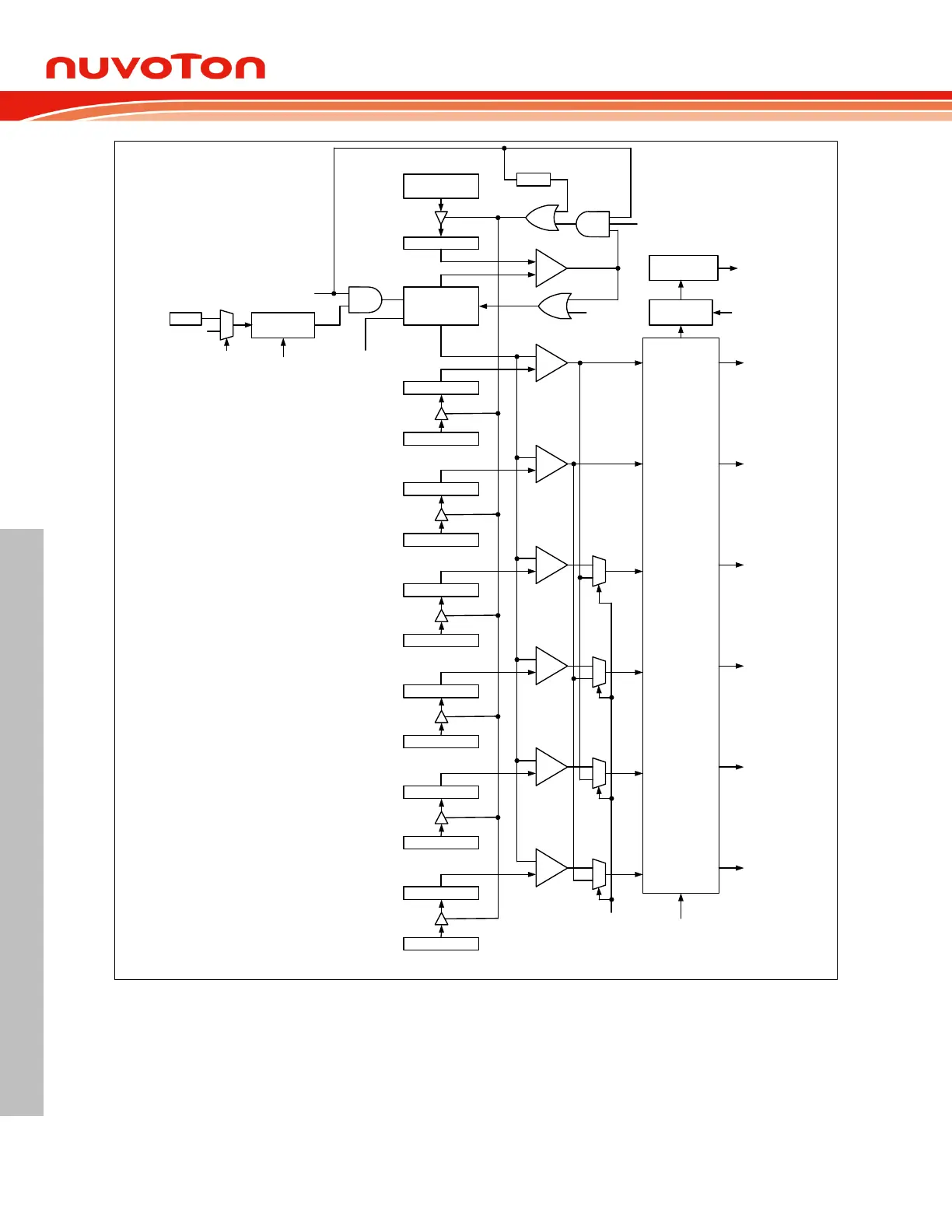

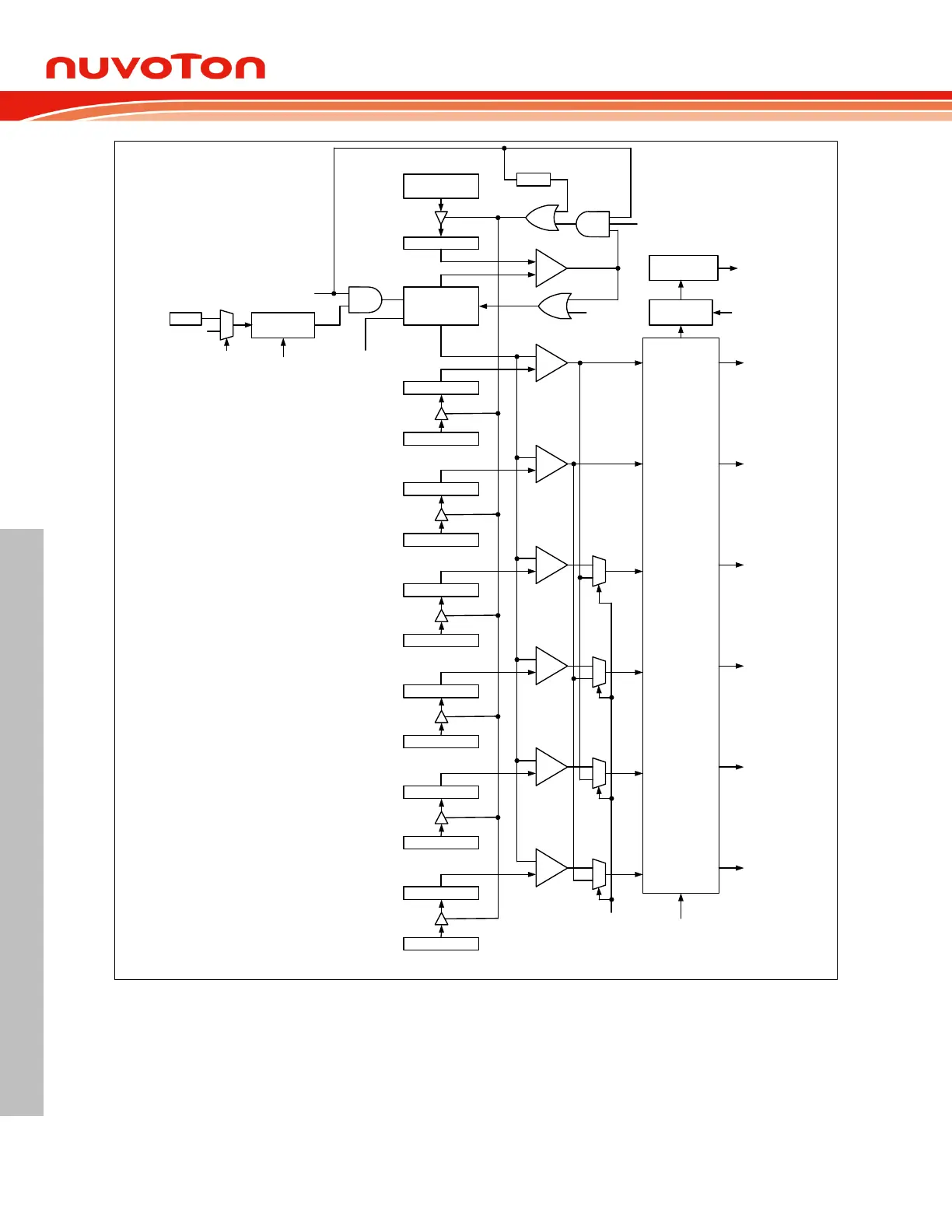

16-bit

up/down

counter

PWM0_CH0

PWM0_CH1

PWM0_CH2

Pre-scalar

INTSEL[1:0], INTTYP[1:0]

(PWMnCON0[3:0])

PWMRUN

(PWM0CON0.7)

CLRPWM

(PWMnCON0.4)

PWM0P

registers

LOAD (PWM0CON0.6)

PWMF

(PWM0CON0.5)

PWM0P buffer

PWM0C0 buffer

PWM0C0 Register

0-to-1

PWM0 and

Fault Brake

output

control

PWMTYP

(PWM0CON1.4)

edge/center

Interrupt

select/type

PWMDIV0[2:0]

(PWM0CON1[2:0])

P0G0

PWM0 interrupt

Brake event

(PWM0_BRAKE)

0

1

Timer 1 overflow

PWMCKS

(CKCON.6)

F

PWM

=

Counter

Matching(edgealigned)/

underflow(venter aligned)

F

SYS

clear counter

=

PWM0C1 buffer

PWM0C1 Register

P0G1

=

PWM0C2 buffer

PWM0C2 Register

=

PWM0C3 buffer

PWM0C3 Register

=

PWM0C4 buffer

PWM0C4 Register

=

PWM0C5 buffer

PWM0C5 Register

=

P0G2

P0G3

P0G4

P0G5

0

1

0

1

0

1

0

1

GP

[PWM0CON1.5]

(PWM0PH,

PWM0PL)

(PWM0CH0H,

PWM0CH0L)

(PWM0CH1H,

PWM0CH1L)

(PWM0CH2H,

PWM0CH2L)

(PWM0CH3H,

PWM0CH3L)

(PWM0CH4H,

PWM0CH4L)

(PWM0CH5H,

PWM0CH5L)

PWM0_CH3

PWM0_CH4

PWM0_CH5

Figure 6.6-1 PWM0 Block Diagram

The PWM0 counter generates six PWM0 signals called P0G0, P0G1, P0G2, P0G3, P0G4, and P0G5.

These signals will go through the PWM0 and Fault Brake output control circuit. It generates real

PWM0 outputs on I/O pins. The output control circuit determines the PWM mode, dead-time insertion,

mask output, Fault Brake control, and PWM polarity. The last stage is a multiplexer of PWM0 output or

I/O function.

The PWM1/2/3 counter generates two PWM1/2/3 signals. These signals will go through the

PWM1/2/3. It generates real PWM1/2/3 outputs on I/O pins. The output control circuit determines the

Loading...

Loading...