MS51

Nov. 28, 2019 Page 329 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

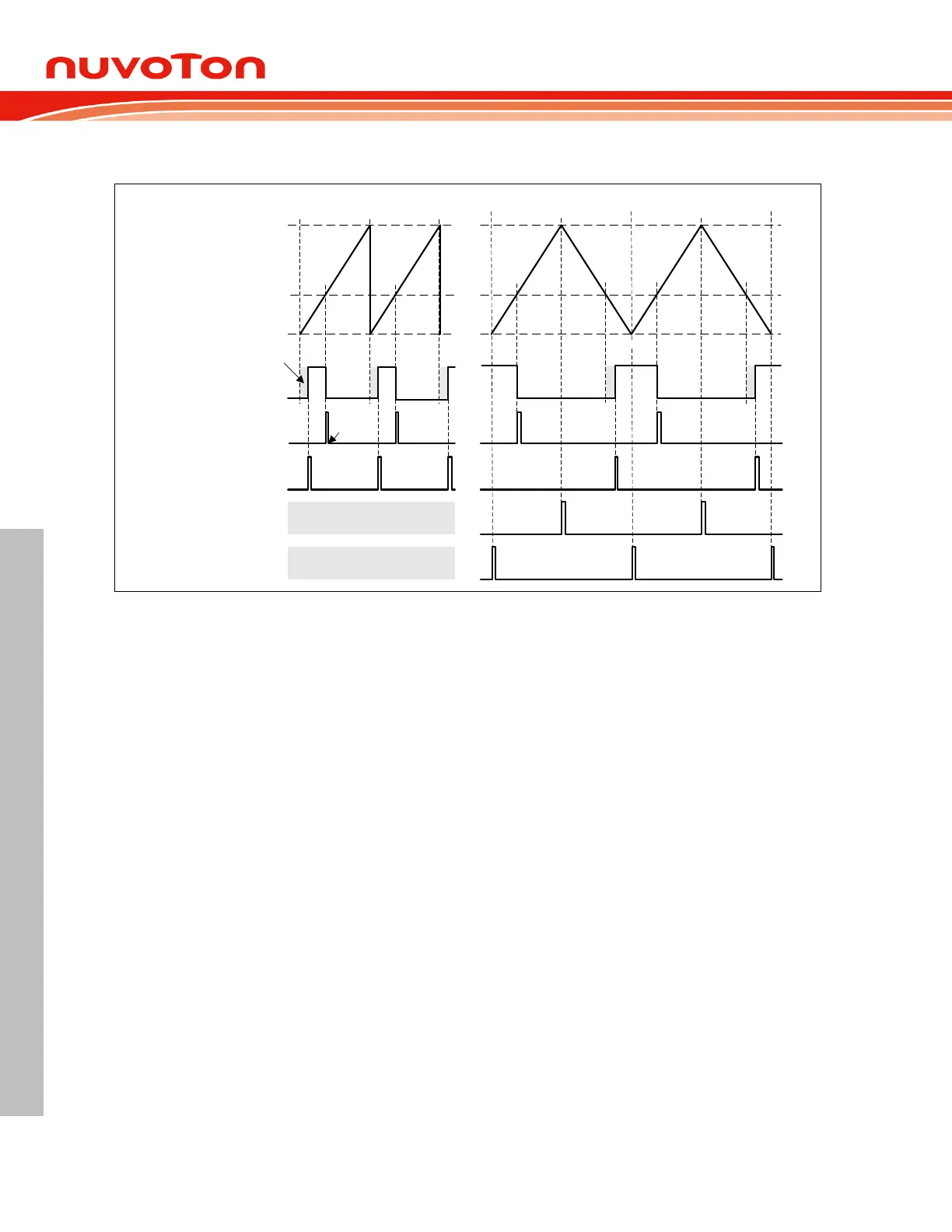

The PWM interrupt related with PWM waveform is shown as figure below.

Reserved

PWMF (central point)

(INTTYP[1:0] = [1:0])

PWMF (end point)

(INTTYP[1:0] = [1:1])

Central point

End point

PWM channel 0/2/4

pin output

Software

clear

12-bit PWM counter

Dead time

PWMF (falling edge)

(INTTYP[1:0] = [0:0])

PWMF (rising edge)

(INTTYP[1:0] = [0:1])

Edge-aligned PWM Center-aligned PWM

Reserved

Figure 6.6-9 PWM Interrupt Type

Fault Brake event requests another interrupt, Fault Brake interrupt. It has different interrupt vector from

PWM interrupt. When either Fault Brake pin input event or ADC compare event occurs, FBF

(PWM0FBD.7) will be set by hardware. It generates Fault Brake interrupt if enabled. The Fault Brake

interrupt enable bit is EFB0 (EIE0.5). FBF Is cleared via software.

Loading...

Loading...