MS51

Nov. 28, 2019 Page 439 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

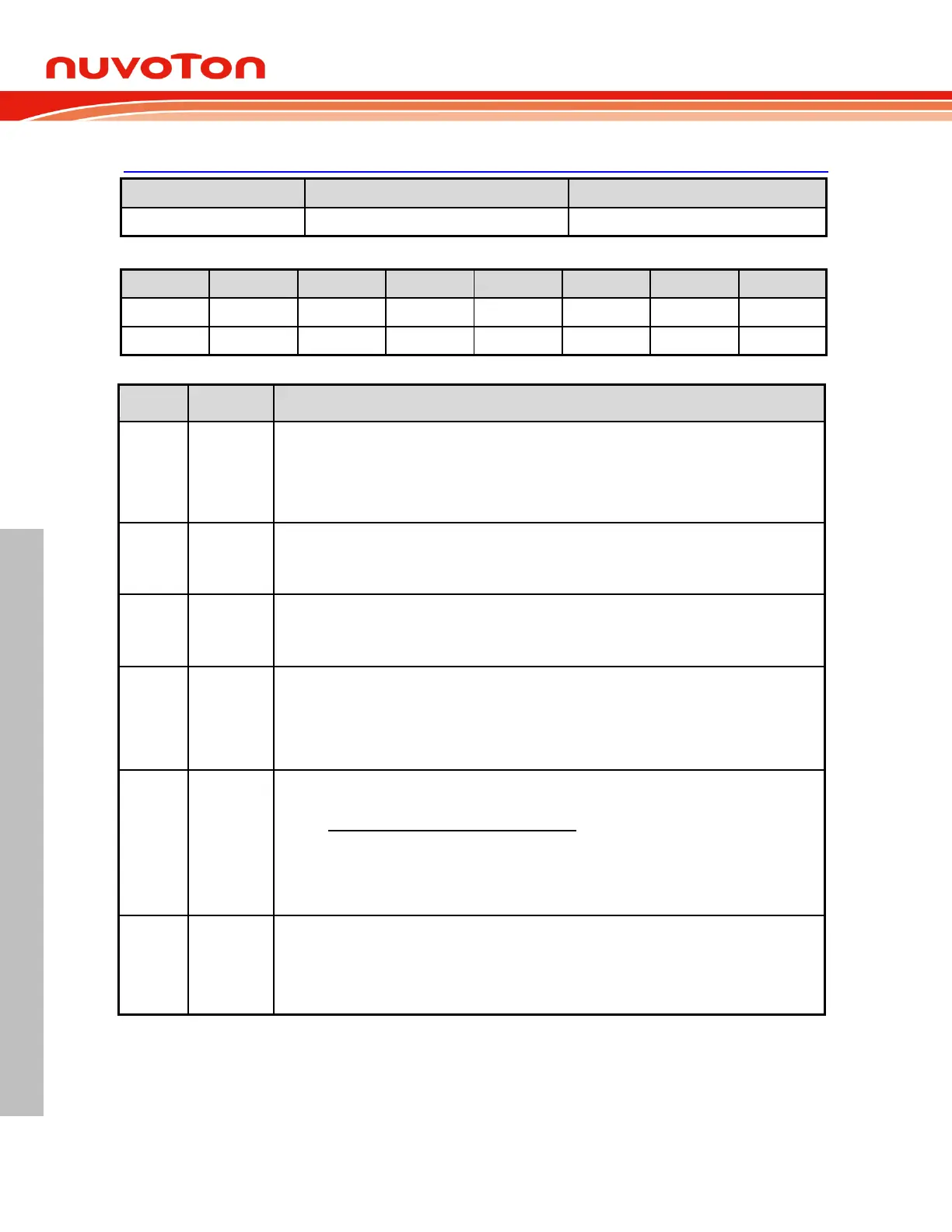

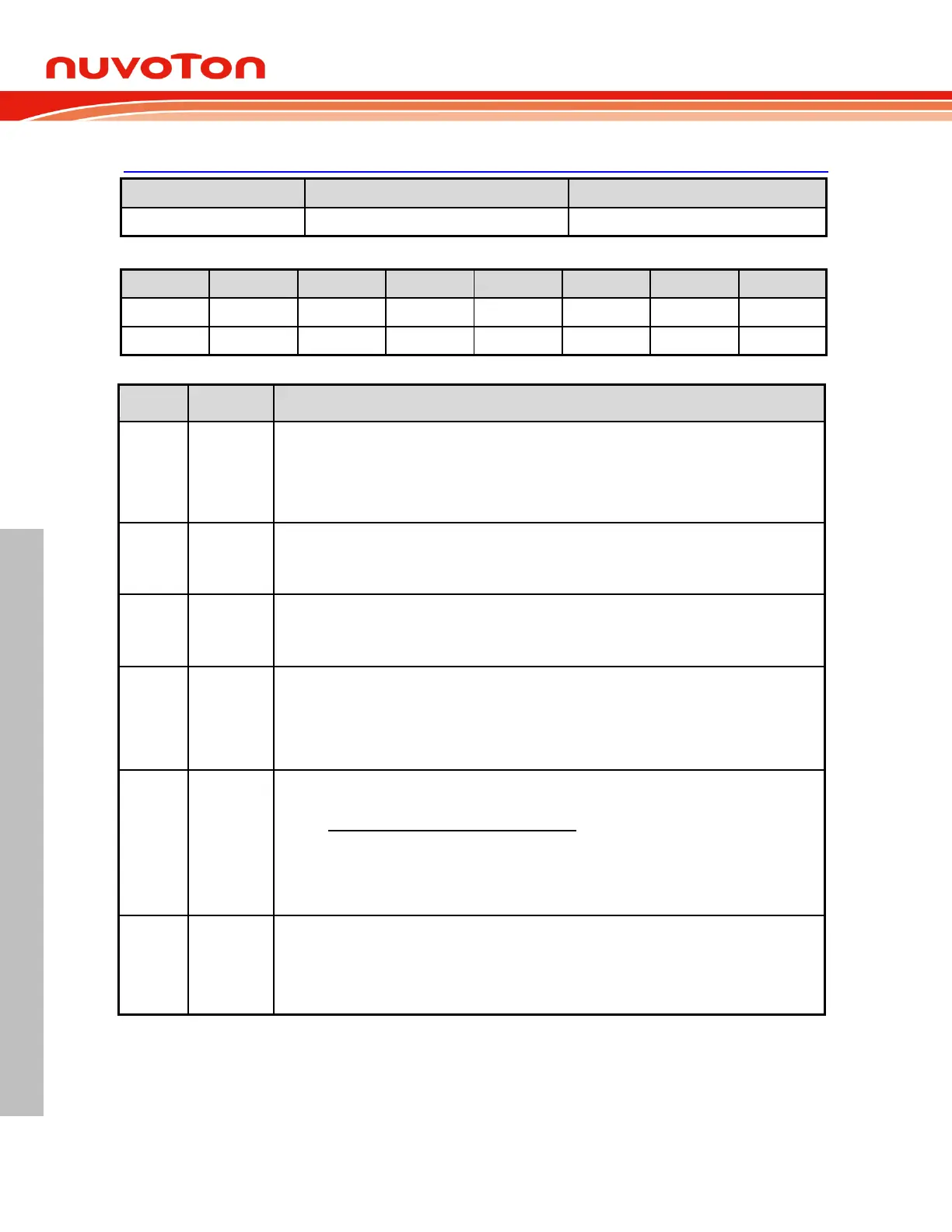

SPSR – Serial Peripheral Status Register

SPI complete flag

This bit is set to logic 1 via hardware while an SPI data transfer is complete or an receiving data

has been moved into the SPI read buffer. If ESPI (EIE .0) and EA are enabled, an SPI interrupt will

be required. This bit should be cleared via software. Attempting to write to SPDR is inhibited if

SPIF is set.

Write collision error flag

This bit indicates a write collision event. Once a write collision event occurs, this bit will be set. It

should be cleared via software.

SPI overrun error flag

This bit indicates an overrun event. Once an overrun event occurs, this bit will be set. If ESPI and

EA are enabled, an SPI interrupt will be required. This bit should be cleared via software.

Mode Fault error flag

This bit indicates a Mode Fault error event. If SS

pin is configured as Mode Fault input (MSTR = 1

and DISMODF = 0) and SS

is pulled low by external devices, a Mode Fault error occurs. Instantly

MODF will be set as logic 1. If ESPI and EA are enabled, an SPI interrupt will be required. This bit

should be cleared via software.

Disable Mode Fault error detection

This bit is used in combination with the SSOE (SPCR.7) bit to determine the feature of SS

pin as

shown in Table 6.12-1 Slave Select Pin Configurations. DISMODF is valid only in Master mode

(MSTR = 1).

0 = Mode Fault detection Enabled. SS

serves as input pin for Mode Fault detection disregard of

SSOE.

1 = Mode Fault detection Disabled. The feature of SS

SPI writer data buffer status

This bit indicates the SPI transmit buffer status.

0 = SPI writer data buffer is empty

1 = SPI writer data buffer is full.

Loading...

Loading...