MS51

Nov. 28, 2019 Page 226 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

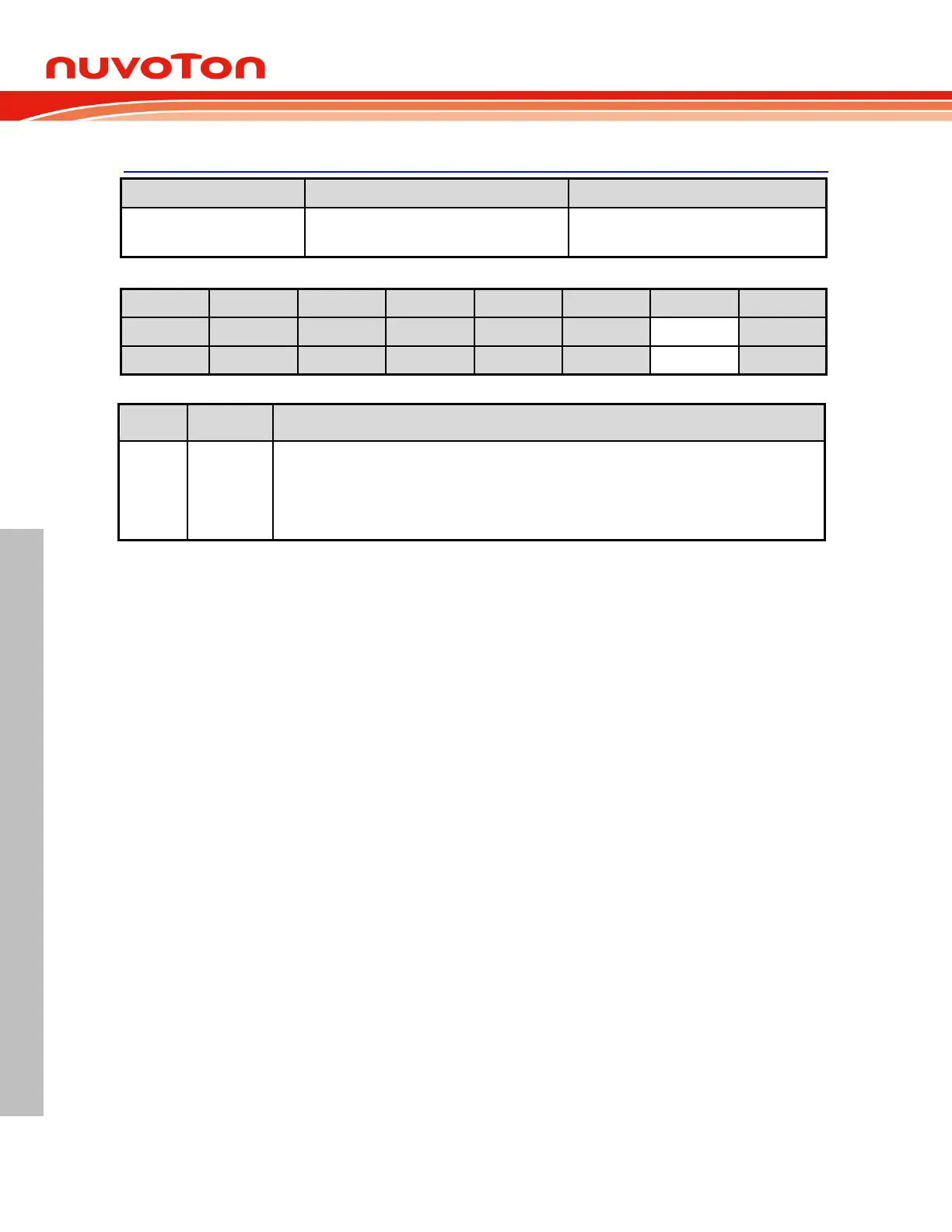

CHPCON – Chip Control

9FH, All page, TA protected

Software 0000_00U0 b

Others 0000_00C0 b

Boot select

This bit defines from which block that MCU re-boots after all resets.

0 = MCU will re-boot from APROM after all resets.

1 = MCU will re-boot from LDROM after all resets.

[1] BS is initialized by being loaded from the inverted value of CBS bit in CONFIG0.7 after resets except software

reset. It keeps unchanged after software reset.

After the MCU is released from reset state, the hardware will always check the BS bit instead of the

CBS bit to determine from which block that the device reboots.

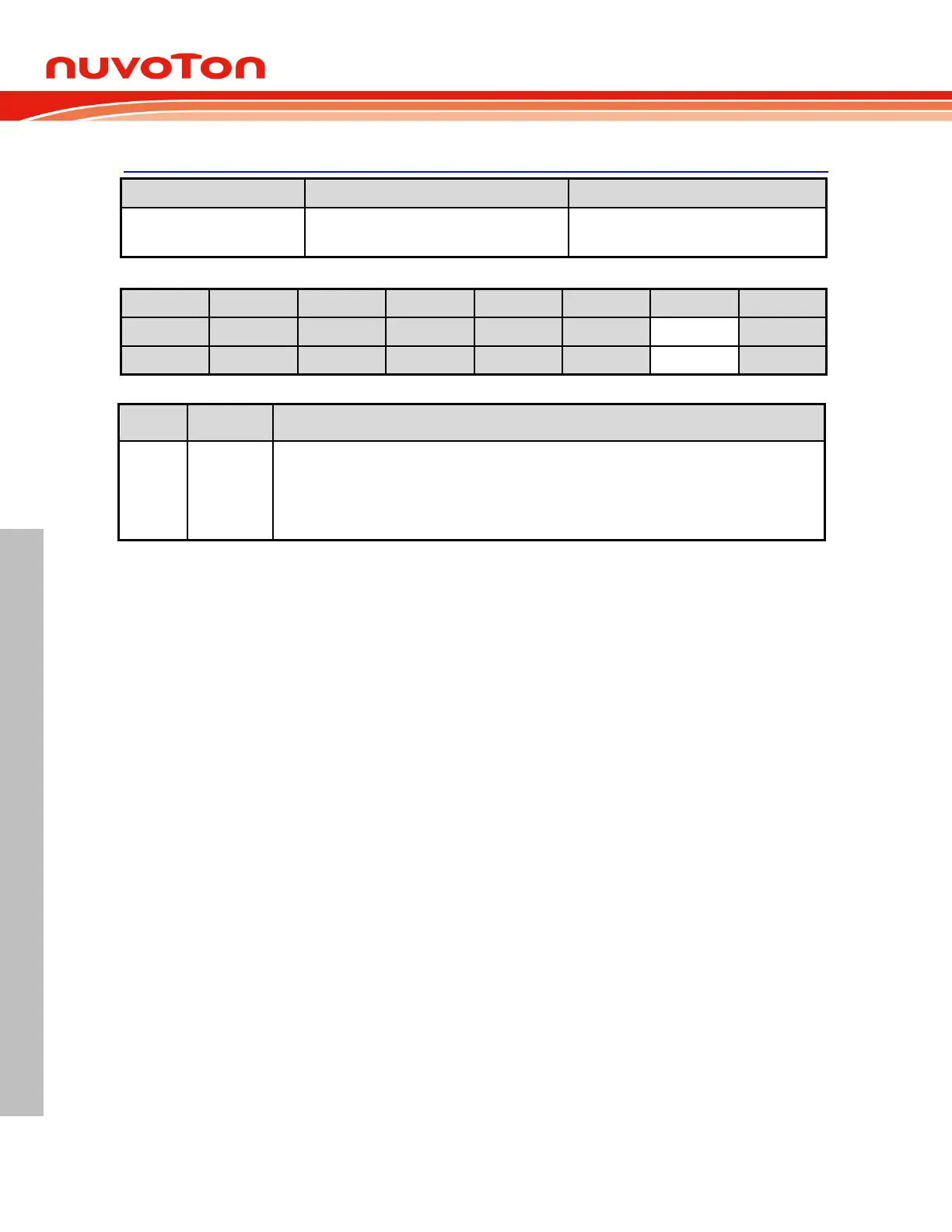

Reset State 6.2.4.8

The reset state besides power-on reset does not affect the on-chip RAM. The data in the RAM will be

preserved during the reset. After the power-on reset the RAM contents will be indeterminate.

After a reset, most of SFR go to their initial values except bits, which are affected by different reset

events.. The Program Counter is forced to 0000H and held as long as the reset condition is applied.

Note that the Stack Pointer is also reset to 07H and thus the stack contents may be effectively lost

during the reset event even though the RAM contents are not altered.

After a reset, all peripherals and interrupts are disabled. The I/O port latches resumes FFH and I/O

mode input-only.

Loading...

Loading...