MS51

Nov. 28, 2019 Page 404 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

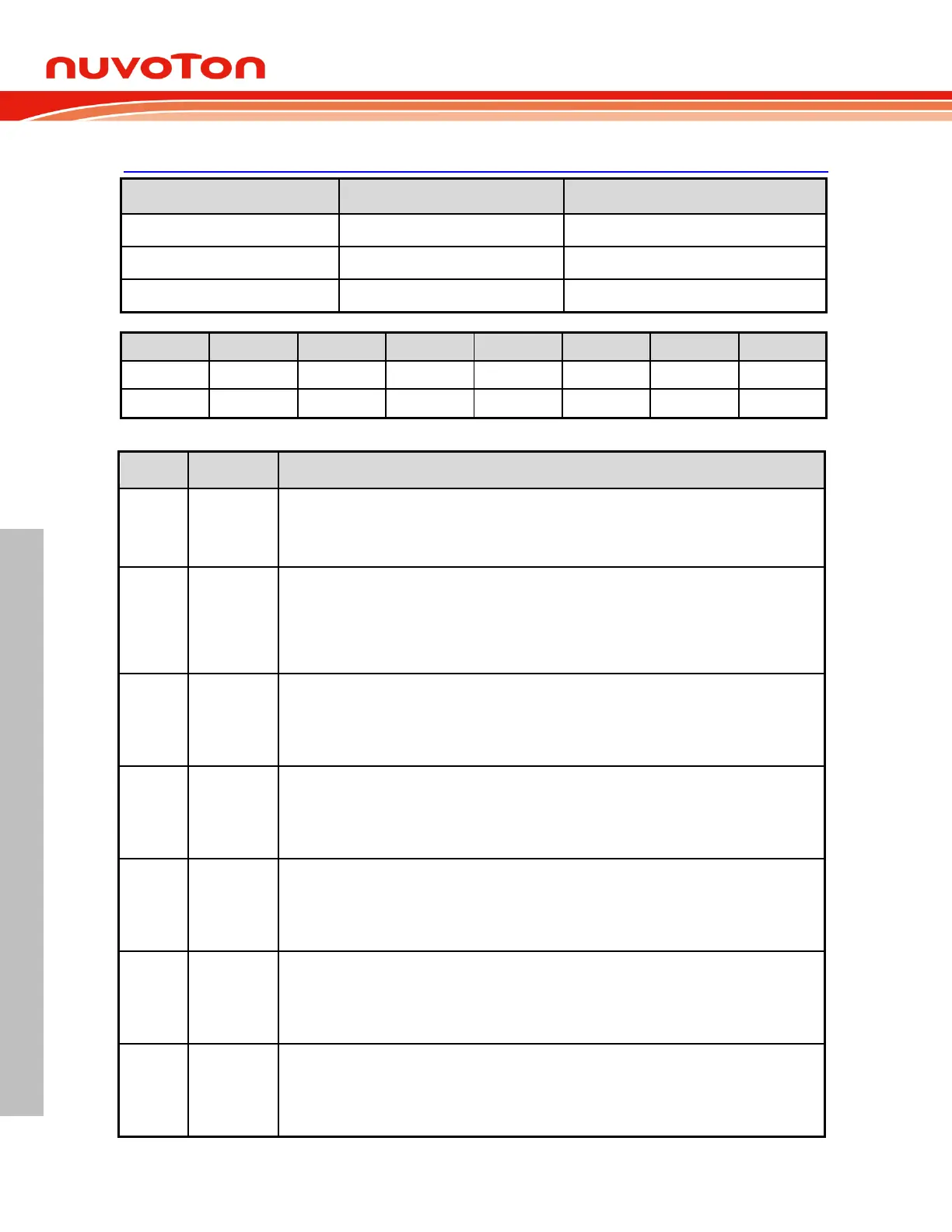

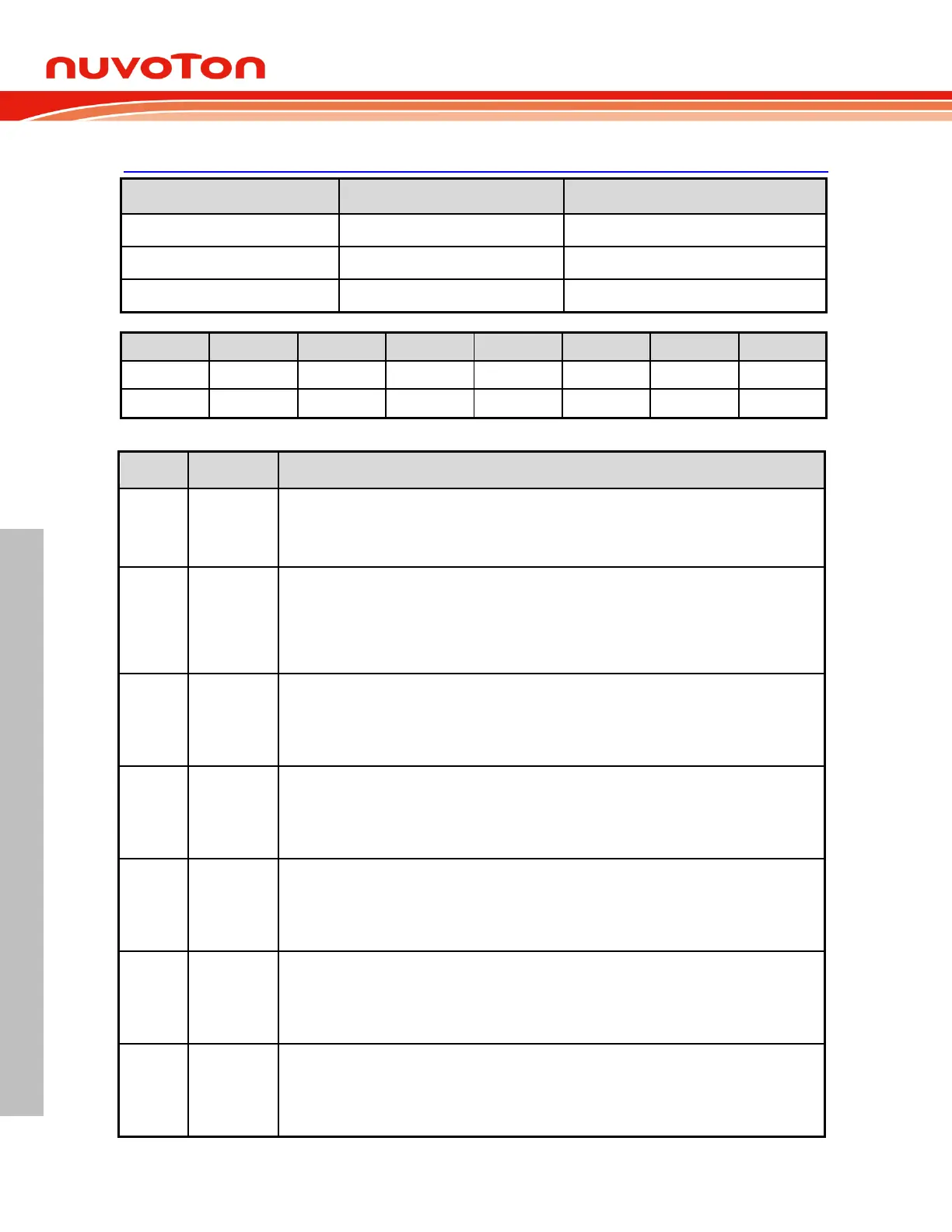

SCnTSR – SC Transfer Status Register

Transmit /Receive in Active Status Flag (Read Only)

0 = This bit is cleared automatically when TX/RX transfer is finished

1 = This bit is set by hardware when TX/RX transfer is in active.

Receiver Break Error Status Flag (Read Only)

This bit is set to logic 1 whenever the received data input (RX) held in the “spacing state” (logic 0)

is longer than a full word transmission time (that is, the total time of “start bit” + data bits + parity +

stop bits). .

Note: This bit is read only, but it can be cleared by writing 0 to it.

Receiver Frame Error Status Flag (Read Only)

This bit is set to logic 1 whenever the received character does not have a valid “stop bit” (that is,

the stop bit following the last data bit or parity bit is detected as logic 0).

Note: This bit is read only, but it can be cleared by writing 0 to it.

Receiver Parity Error Status Flag (Read Only)

This bit is set to logic 1 whenever the received character does not have a valid

“parity bit”.

Note: This bit is read only, but it can be cleared by writing 0 to it.

Transmit Buffer Empty Status Flag (Read Only)

This bit indicates TX buffer empty or not.

Note: When TX buffer has been transferred to Transmitter Shift Register, hardware sets this bit

high. It will be cleared when writing data into DAT(SCnDR[7:0]) (TX buffer not empty).

TX Overflow Error Interrupt Status Flag (Read Only)

If TX buffer is full, an additional write to DAT(SCnDR[7:0]) will cause this bit be set to “1” by

hardware.

Note: This bit is read only, but it can be cleared by writing 0 to it.

Receiver Buffer Empty Status Flag(Read Only)

This bit indicates RX buffer empty or not.

Note: When Rx buffer has been read by CPU, hardware sets this bit high. It will be cleared when

SC receives any new data.

Loading...

Loading...