MS51

Nov. 28, 2019 Page 423 of 491 Rev 1.00

MS51 32K SERIES TECHNICAL REFERENCE MANUAL

6.11.6 Control Registers of I

2

C

There are five control registers to interface the I

2

C bus including I2CON, I2STAT, I2DAT, I2ADDR, and

I2CLK. These registers provide protocol control, status, data transmitting and receiving functions, and

clock rate configuration. For application flexibility, I2C0_SDA and I2C0_SCL pins can be exchanged

by I2CPX (I2CON.0). The following registers relate to I

2

C function.

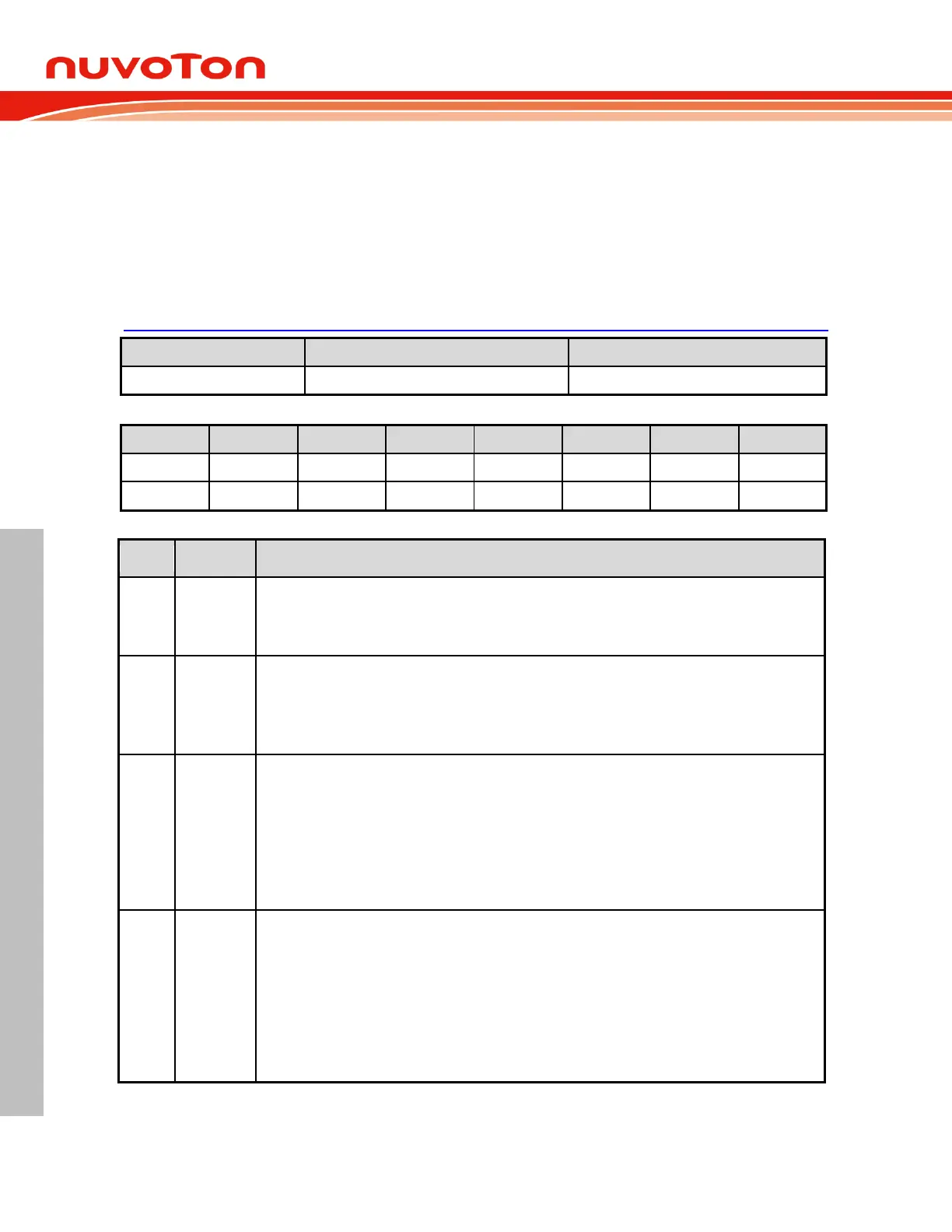

I2CON – I

2

C Control

C0H, All pages, Bit addressable

I2C0 hold time extend enable

0 = I

2

C DATA to I2C0_SCL hold time extend disabled

1 = I

2

C DATA to I2C0_SCL hold time extend enabled, extend 8 system clock

I

2

C bus enable

0 = I

2

C bus Disabled.

1 = I

2

C bus Enabled.

Before enabling the I

2

C, I2C0_SCL and I2C0_SDA port latches should be set to logic 1.

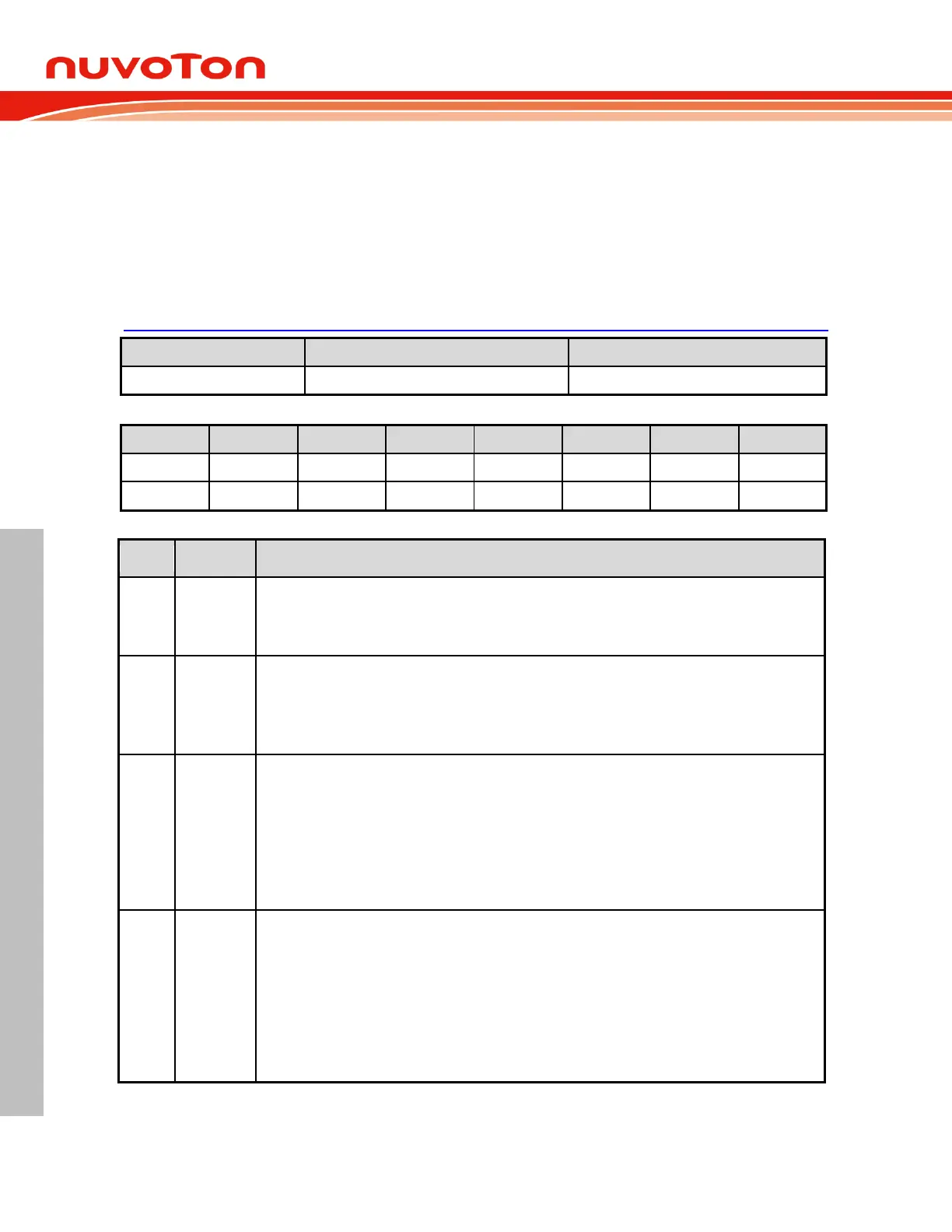

START flag

When STA is set, the I

2

C generates a START condition if the bus is free. If the bus is busy, the I

2

C

waits for a STOP condition and generates a START condition following.

If STA is set while the I

2

C is already in the master mode and one or more bytes have been transmitted

or received, the I

2

C generates a repeated START condition.

Note that STA can be set anytime evenin a slave mode, but STA is not hardware automatically

cleared after START or repeated START condition has been detected. User should take care of it by

clearing STA manually.

STOP flag

When STO is set if the I

2

C is in the master mode, a STOP condition is transmitted to the bus. STO is

automatically cleared by hardware once the STOP condition has been detected on the bus.

The STO flag setting is also used to recover the I

2

C device from the bus error state (I2STAT as 00H).

In this case, no STOP condition is transmitted to the I

2

C bus.

If the STA and STO bits are both set and the device is original in the master mode, the I

2

C bus will

generate a STOP condition and immediately follow a START condition. If the device is in slave mode,

STA and STO simultaneous setting should be avoid from issuing illegal I

2

C frames.

Loading...

Loading...