3. Startup time is defined as the time taken by LVDS receiver for settling after its pwr_down (power down) has been

deasserted. Here it is assumed that current reference is already stable (see Bias start-up time). LVDS functionality is

guaranteed only after the startup time.

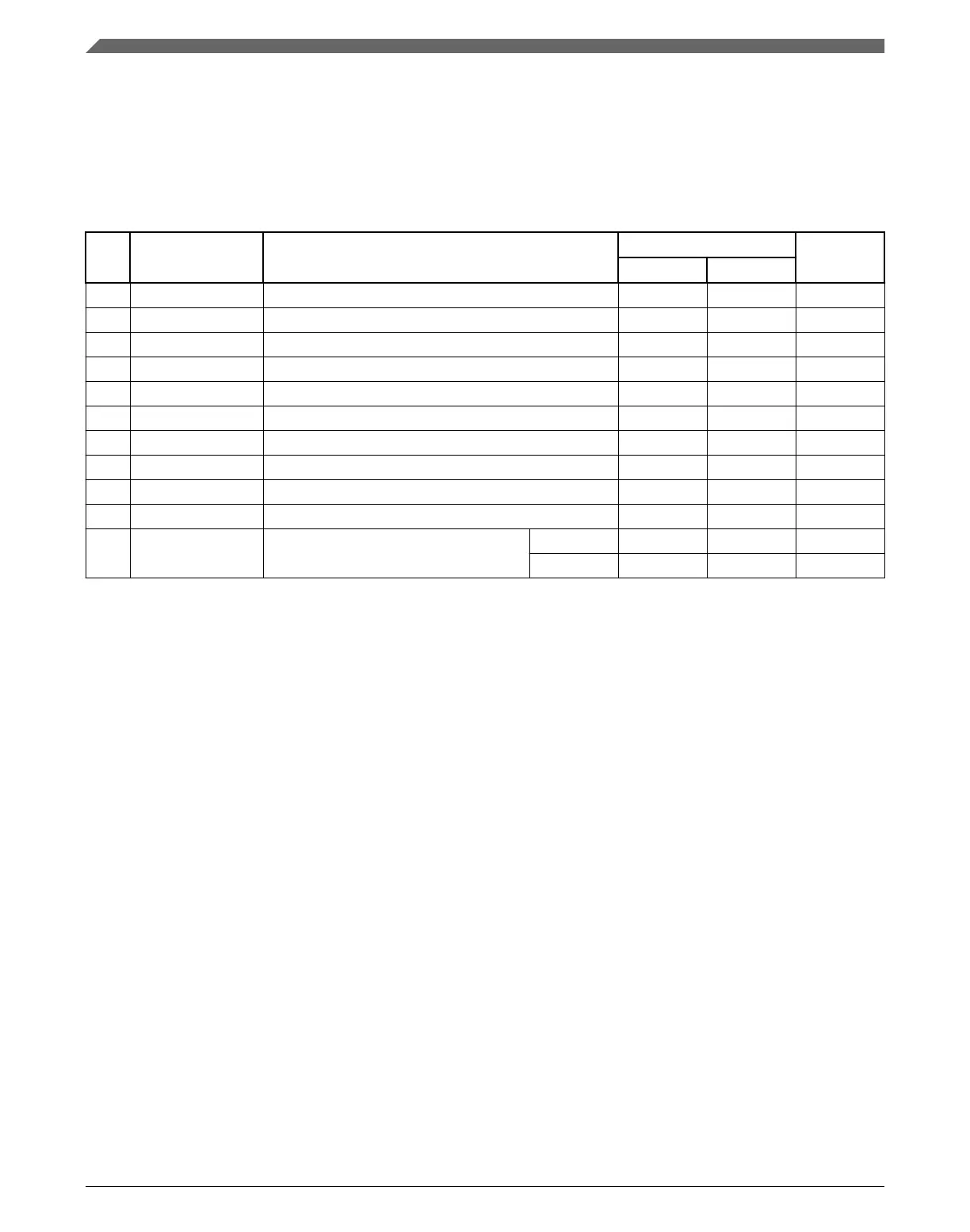

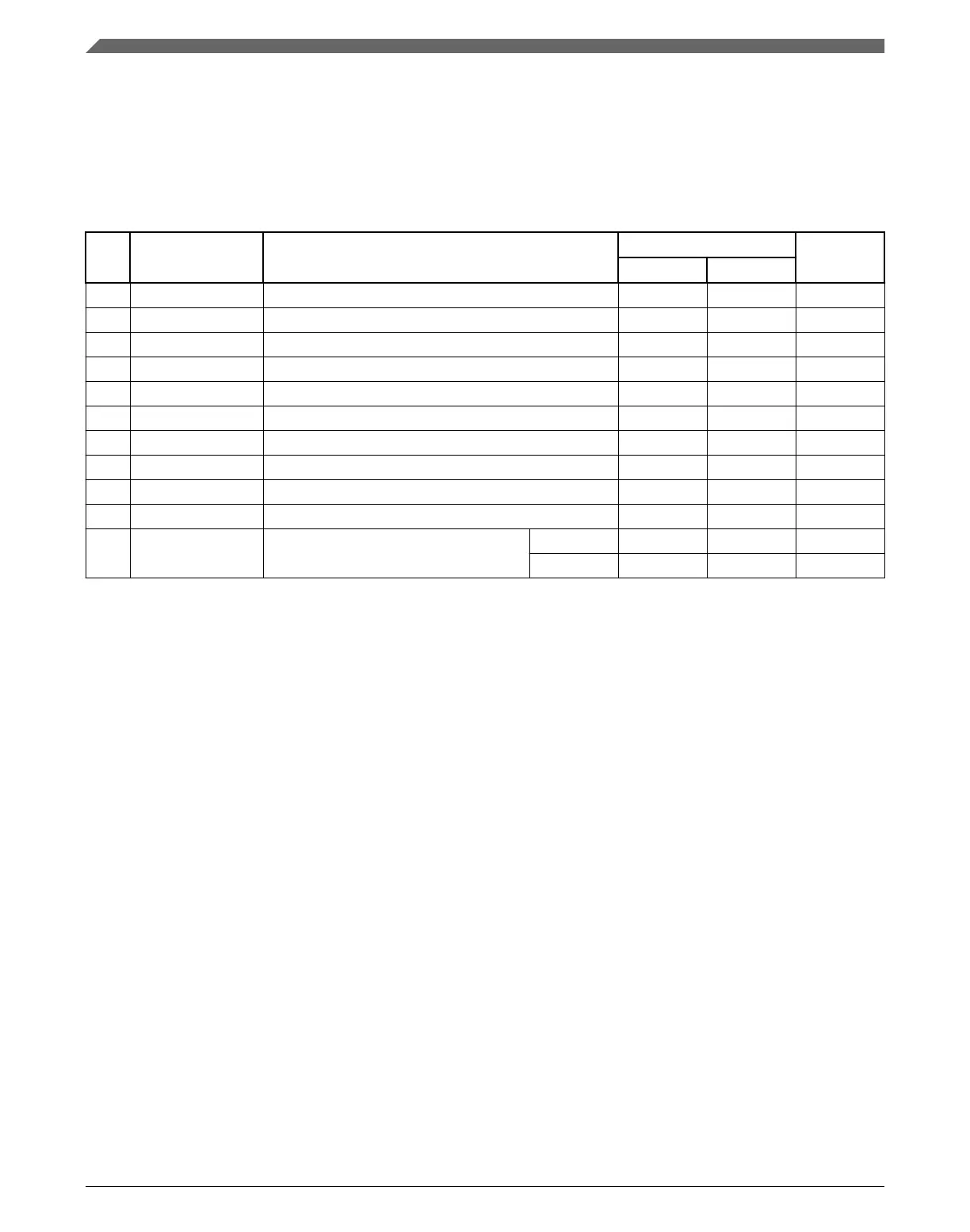

18.1.3.1 Aurora debug port timing

Table 38. Aurora debug port timing

# Symbol Parameter

Value

Unit

Min Max

1 t

REFCLK

Reference clock frequency 625 1200 MHz

1a t

MCYC

Reference clock rise/fall time — 400 ps

2 t

RCDC

Reference clock duty cycle 45 55 %

3 J

RC

Reference clock jitter — 40 ps

4 t

STABILITY

Reference clock stability 50 — PPM

5 BER Bit error rate — 10

-12

—

6 J

D

Transmit lane deterministic jitter — 0.17 OUI

7 J

T

Transmit lane total jitter — 0.35 OUI

8 S

O

Differential output skew — 20 ps

9 S

MO

Lane to lane output skew — 1000 ps

10 OUI Aurora lane unit interval

1

625 Mbps 1600 1600 ps

1.25Gbps 800 800 ps

1. ± 100 PPM

AC specifications

SPC5746R Microcontroller Data Sheet, Rev. 6, 06/2017

64 NXP Semiconductors

Loading...

Loading...