5-10 Riverstone Networks RS 3000/3100/3200 Switch Router Getting Started Guide

Upgrading FPGA Code Managing Software

3. After the FPGA upgrade process completes, the line card starts passing traffic.

Notice in the example above that the hot swapping out and in occurs as part of the upgrade process – and does not have

to be performed after the upgrade.

5.4.2 Upgrading FPGA Code from Flash RAM

FPGA code can be downloaded directly from the flash RAM residing within the Control Module. In this example, the

FPGA code is downloaded from a network TFTP server and copied directly to the flash RAM in

slot0 of the Control

Module. Once copied to the flash RAM, the upgrade is performed using the image on the flash RAM in

slot0.

1. Load the FPGA code files onto the TFTP server. Make sure that the RS can reach the server across

the network.

Enter the

system linecard upgrade command, specifying the IP address of the TFTP server, the full path and

filename of the FPGA code, and the slot number:

slot0.

2. Use the system linecard list-images command to see the FPGA code that has been copied

to the flash RAM.

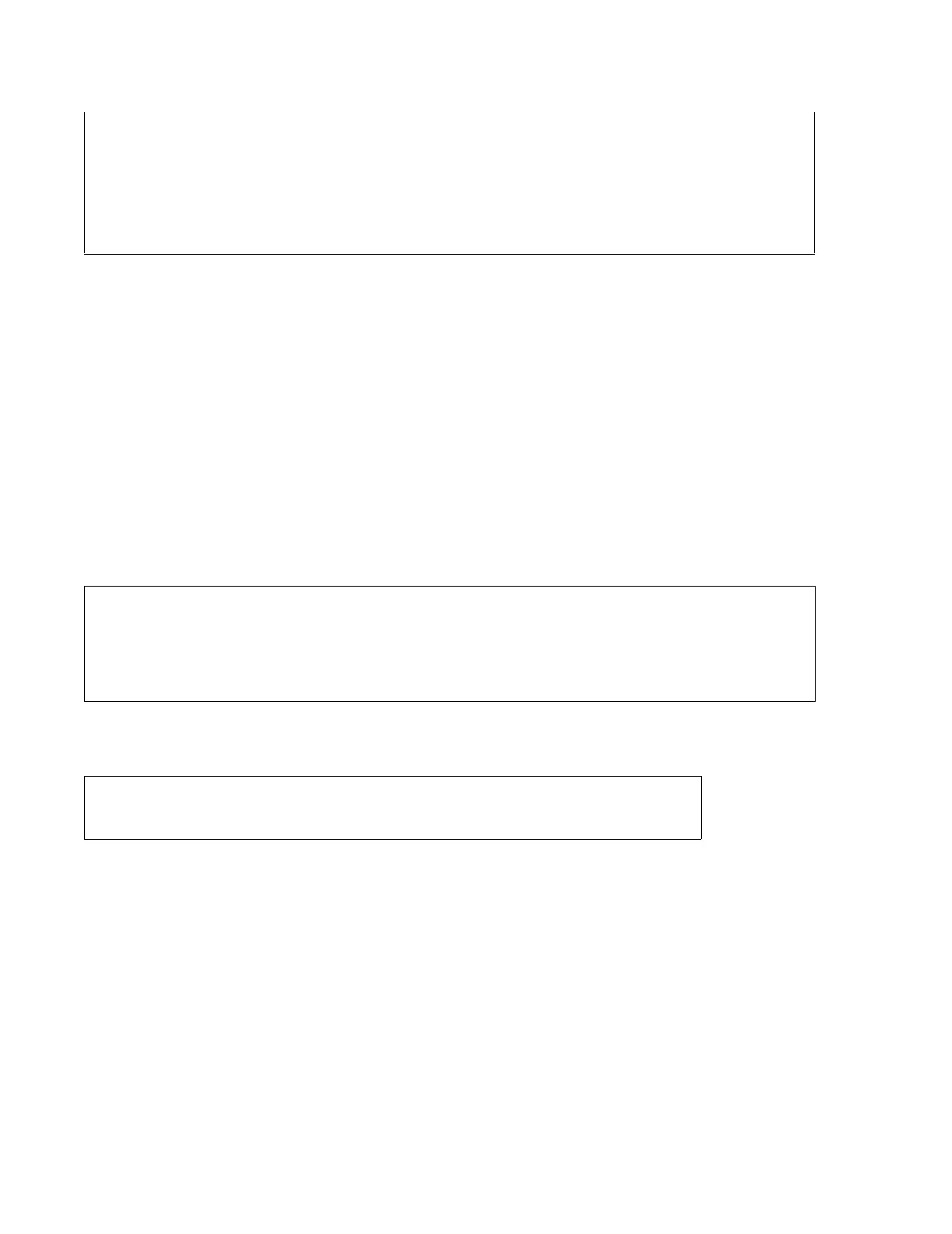

2002-05-30 14:08:37 %SYS-I-HOTSWAP_INRXD, received hotswapped-in

request for slot 6, detecting, please wait

2002-05-30 14:08:44 %SYS-I-DSCVMOD, discovered '2-POS OC12 "M"' module in slot 2

2002-05-30 14:08:47 %SYS-I-INITPORT, initialized slot 2, port 1

2002-05-30 14:08:47 %SYS-I-INITPORT, initialized slot 2, port 2

2002-05-30 14:08:52 %SYS-I-HOTSWAPIN, module in slot 2 is hotswapped in

rs#

rs# system linecard upgrade 10.50.89.88 posrel/oc12_mpls_38k/oc12mr38.000 slot0

Downloading package 'posrel/oc12_mpls_8k/oc12mr8x.000' from host '10.50.89.88'

download: done

Writing package 'oc12mr8x.000' to '/pc-flash0/linecard'

save: done

rs#

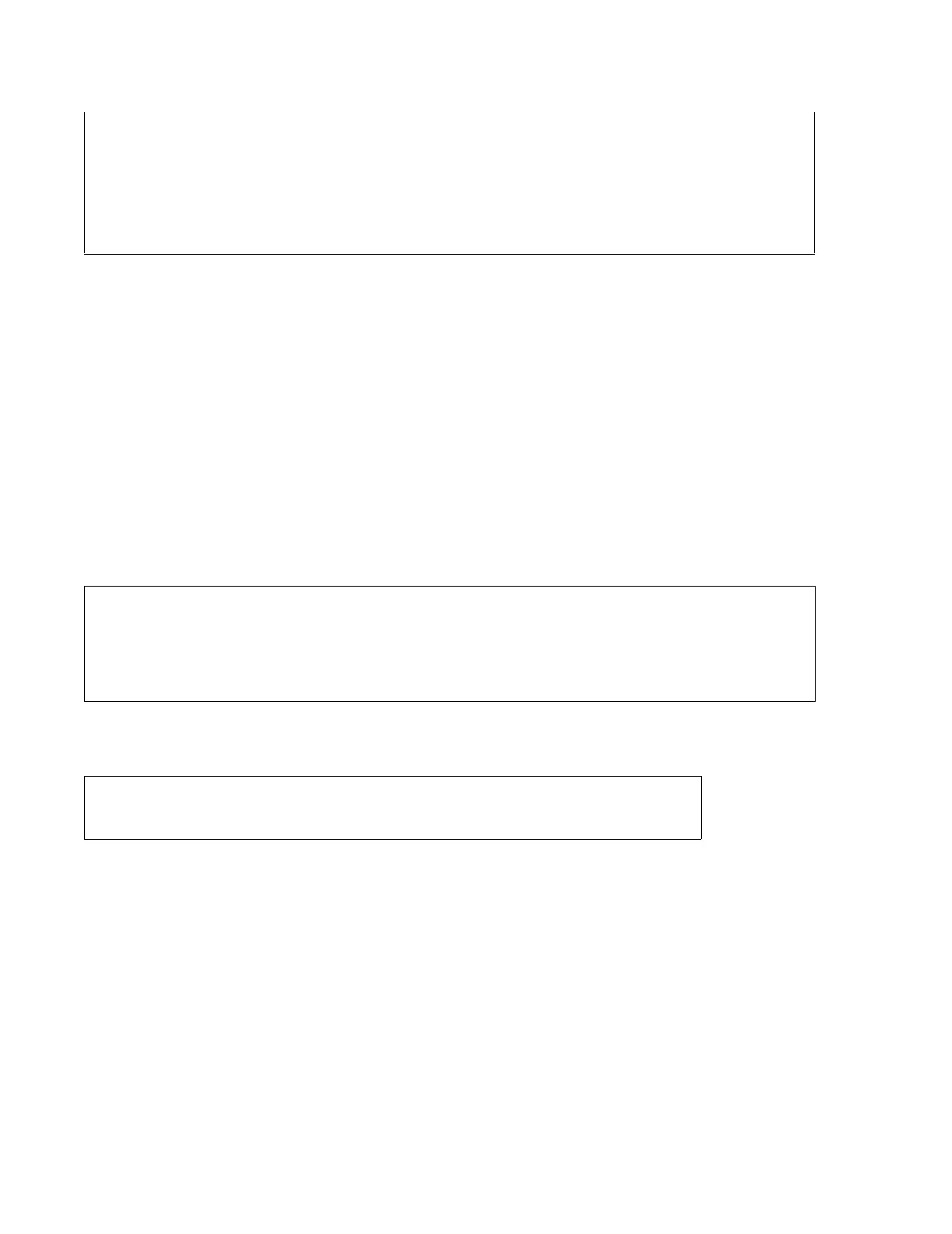

rs# system linecard list-images

slot0: oc12mr8x.000

rs#

Loading...

Loading...