DocID13902 Rev 15 650/1128

RM0008 Controller area network (bxCAN)

689

bxCAN can be woken up (exit Sleep mode) either by software clearing the SLEEP bit or on

detection of CAN bus activity.

On CAN bus activity detection, hardware automatically performs the wakeup sequence by

clearing the SLEEP bit if the AWUM bit in the CAN_MCR register is set. If the AWUM bit is

cleared, software has to clear the SLEEP bit when a wakeup interrupt occurs, in order to exit

from Sleep mode.

Note: If the wakeup interrupt is enabled (WKUIE bit set in CAN_IER register) a wakeup interrupt

will be generated on detection of CAN bus activity, even if the bxCAN automatically

performs the wakeup sequence.

After the SLEEP bit has been cleared, Sleep mode is exited once bxCAN has synchronized

with the CAN bus, refer to Figure 223: bxCAN operating modes. The Sleep mode is exited

once the SLAK bit has been cleared by hardware.

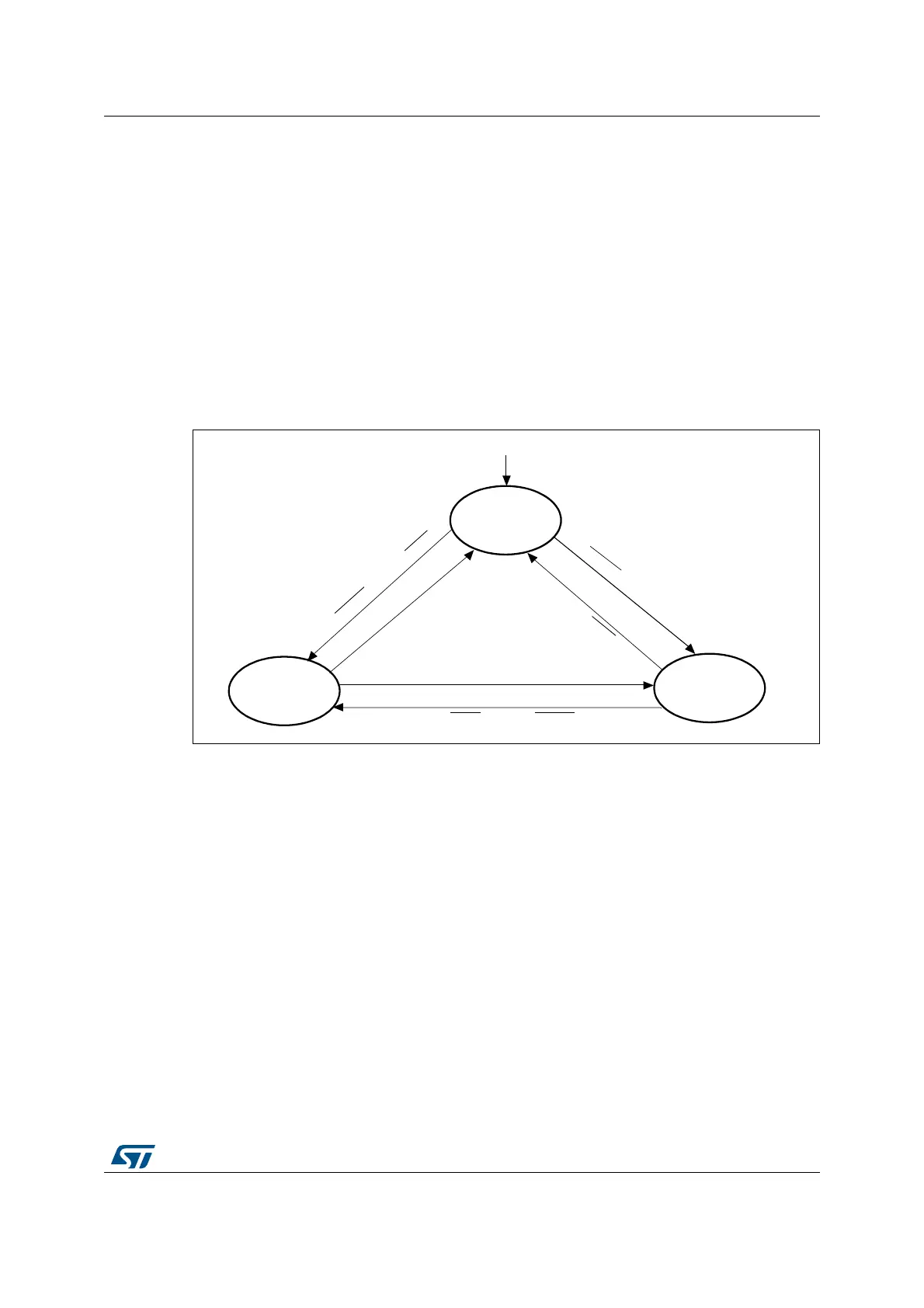

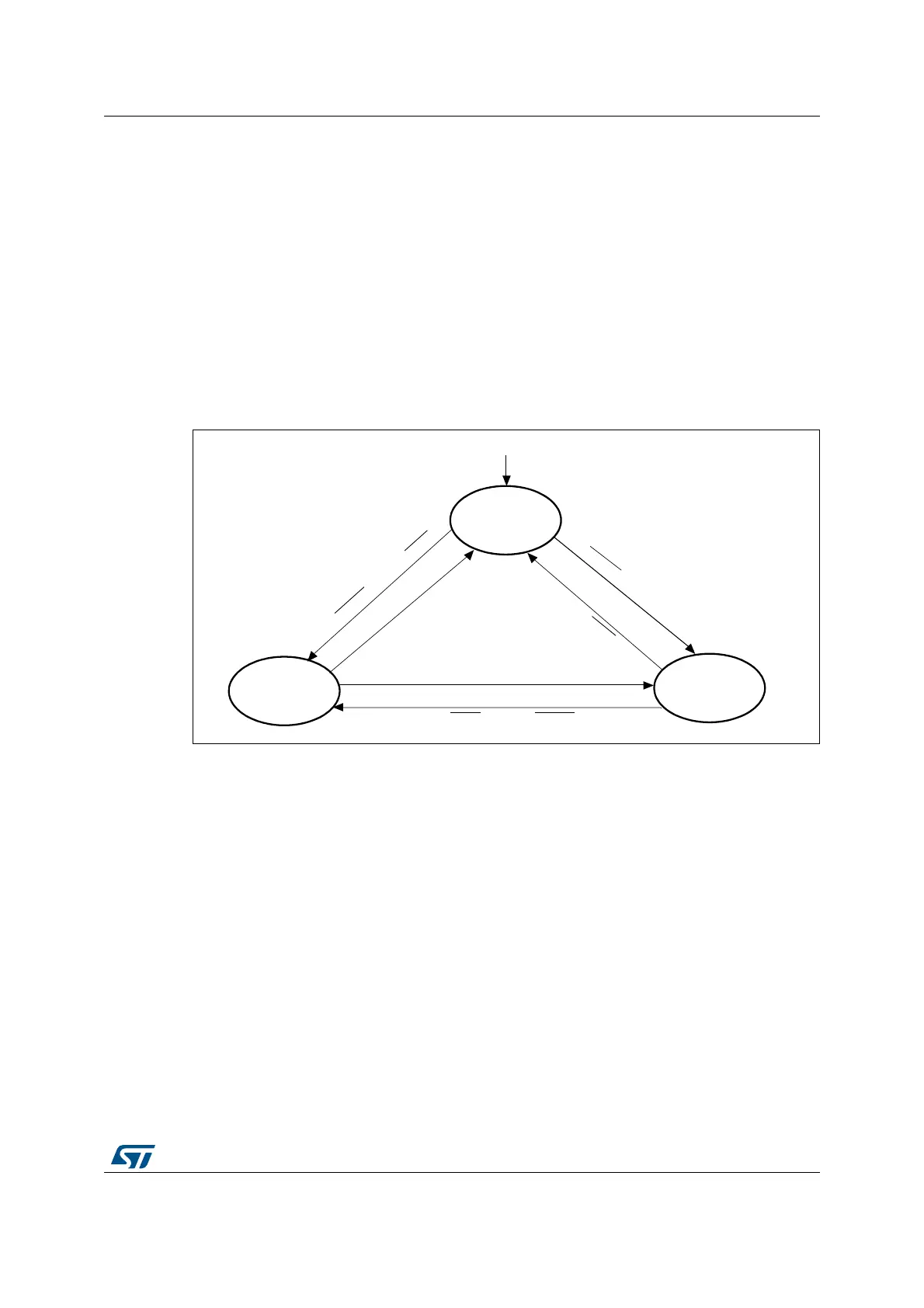

Figure 223. bxCAN operating modes

1. ACK = The wait state during which hardware confirms a request by setting the INAK or SLAK bits in the

CAN_MSR register

2. SYNC = The state during which bxCAN waits until the CAN bus is idle, meaning 11 consecutive recessive

bits have been monitored on CANRX

24.5 Test mode

Test mode can be selected by the SILM and LBKM bits in the CAN_BTR register. These bits

must be configured while bxCAN is in Initialization mode. Once test mode has been

selected, the INRQ bit in the CAN_MCR register must be reset to enter Normal mode.

24.5.1 Silent mode

The bxCAN can be put in Silent mode by setting the SILM bit in the CAN_BTR register.

In Silent mode, the bxCAN is able to receive valid data frames and valid remote frames, but

it sends only recessive bits on the CAN bus and it cannot start a transmission. If the bxCAN

has to send a dominant bit (ACK bit, overload flag, active error flag), the bit is rerouted

internally so that the CAN Core monitors this dominant bit, although the CAN bus may

3LEEP

)NITIALIZATION

.ORMAL

2ESET

3,!+

).!+

3,!+

).!+

3,!+

).!+

3

,

%

%

0

)

.

2

1

!

#

+

3

,

%

%

0

)

.

2

1

!

#

+

).21!#+

).21

39.#3,%%0

3

,

%

%

0

!

#

+

3

,

%

%

0

3

9

.

#

)

.

2

1

AI

Loading...

Loading...