Analog-to-digital converter (ADC) RM0008

221/1128 DocID13902 Rev 15

11.3.9 Injected channel management

Triggered injection

To use triggered injection, the JAUTO bit must be cleared and SCAN bit must be set in the

ADC_CR1 register.

1. Start conversion of a group of regular channels either by external trigger or by setting

the ADON bit in the ADC_CR2 register.

2. If an external injected trigger occurs during the regular group channel conversion, the

current conversion is reset and the injected channel sequence is converted in Scan

once mode.

3. Then, the regular group channel conversion is resumed from the last interrupted

regular conversion. If a regular event occurs during an injected conversion, it doesn’t

interrupt it but the regular sequence is executed at the end of the injected sequence.

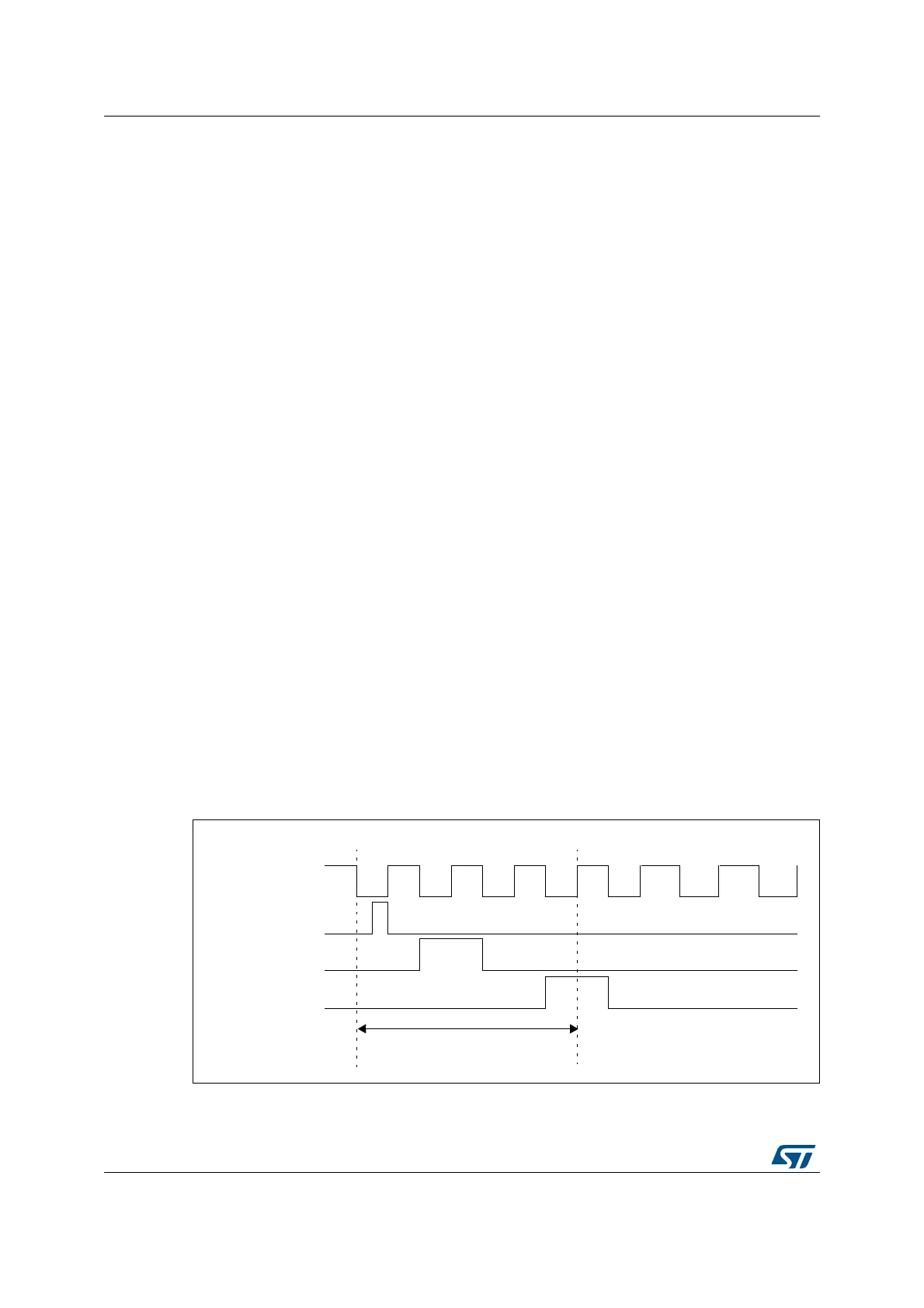

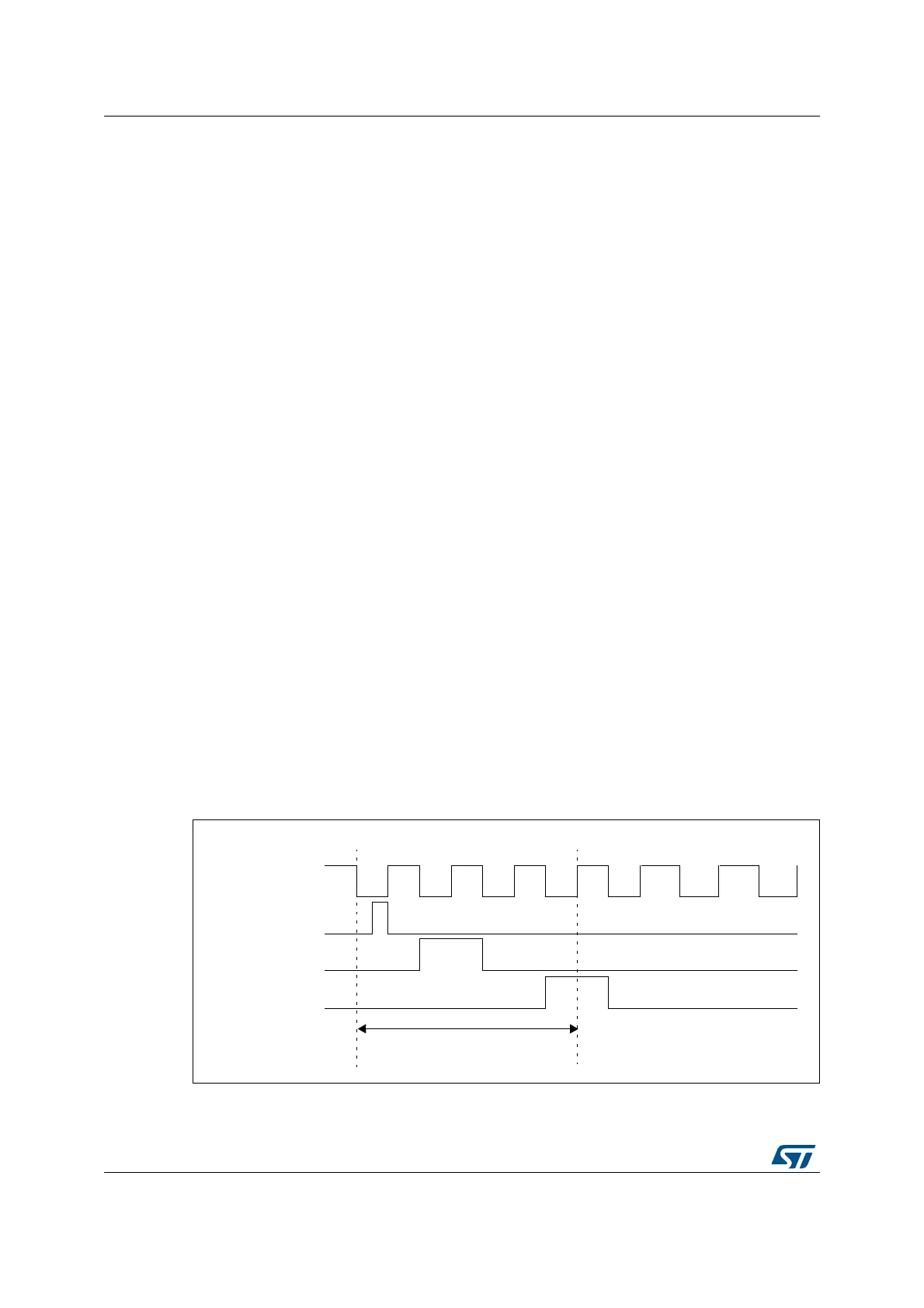

Figure 25 shows the timing diagram.

Note: When using triggered injection, the interval between trigger events must be longer than the

injection sequence. For instance, if the sequence length is 28 ADC clock cycles (that is two

conversions with a 1.5 clock-period sampling time), the minimum interval between triggers

must be 29 ADC clock cycles.

Auto-injection

If the JAUTO bit is set, then the injected group channels are automatically converted after

the regular group channels. This can be used to convert a sequence of up to 20 conversions

programmed in the ADC_SQRx and ADC_JSQR registers.

In this mode, external trigger on injected channels must be disabled.

If the CONT bit is also set in addition to the JAUTO bit, regular channels followed by injected

channels are continuously converted.

For ADC clock prescalers ranging from 4 to 8, a delay of 1 ADC clock period is automatically

inserted when switching from regular to injected sequence (respectively injected to regular).

When the ADC clock prescaler is set to 2, the delay is 2 ADC clock periods.

Note: It is not possible to use both auto-injected and discontinuous modes simultaneously.

Figure 25. Injected conversion latency

1. The maximum latency value can be found in the electrical characteristics of the STM32F101xx and

STM32F103xx datasheets.

ADC clock

Inj. event

Reset ADC

SOC

max latency

(1)

Loading...

Loading...