DocID13902 Rev 15 74/1128

RM0008 Power control (PWR)

80

5.3.4 Stop mode

The Stop mode is based on the Cortex

®

-M3 deepsleep mode combined with peripheral

clock gating. The voltage regulator can be configured either in normal or low-power mode.

In Stop mode, all clocks in the 1.8 V domain are stopped, the PLL, the HSI and the HSE RC

oscillators are disabled. SRAM and register contents are preserved.

In the Stop mode, all I/O pins keep the same state as in the Run mode.

Entering Stop mode

Refer to Table 1 4 for details on how to enter the Stop mode.

To further reduce power consumption in Stop mode, the internal voltage regulator can be put

in low-power mode. This is configured by the LPDS bit of the Power control register

(PWR_CR).

If Flash memory programming is ongoing, the Stop mode entry is delayed until the memory

access is finished.

If an access to the APB domain is ongoing, The Stop mode entry is delayed until the APB

access is finished.

In Stop mode, the following features can be selected by programming individual control bits:

• Independent watchdog (IWDG): the IWDG is started by writing to its Key register or by

hardware option. Once started it cannot be stopped except by a Reset. See

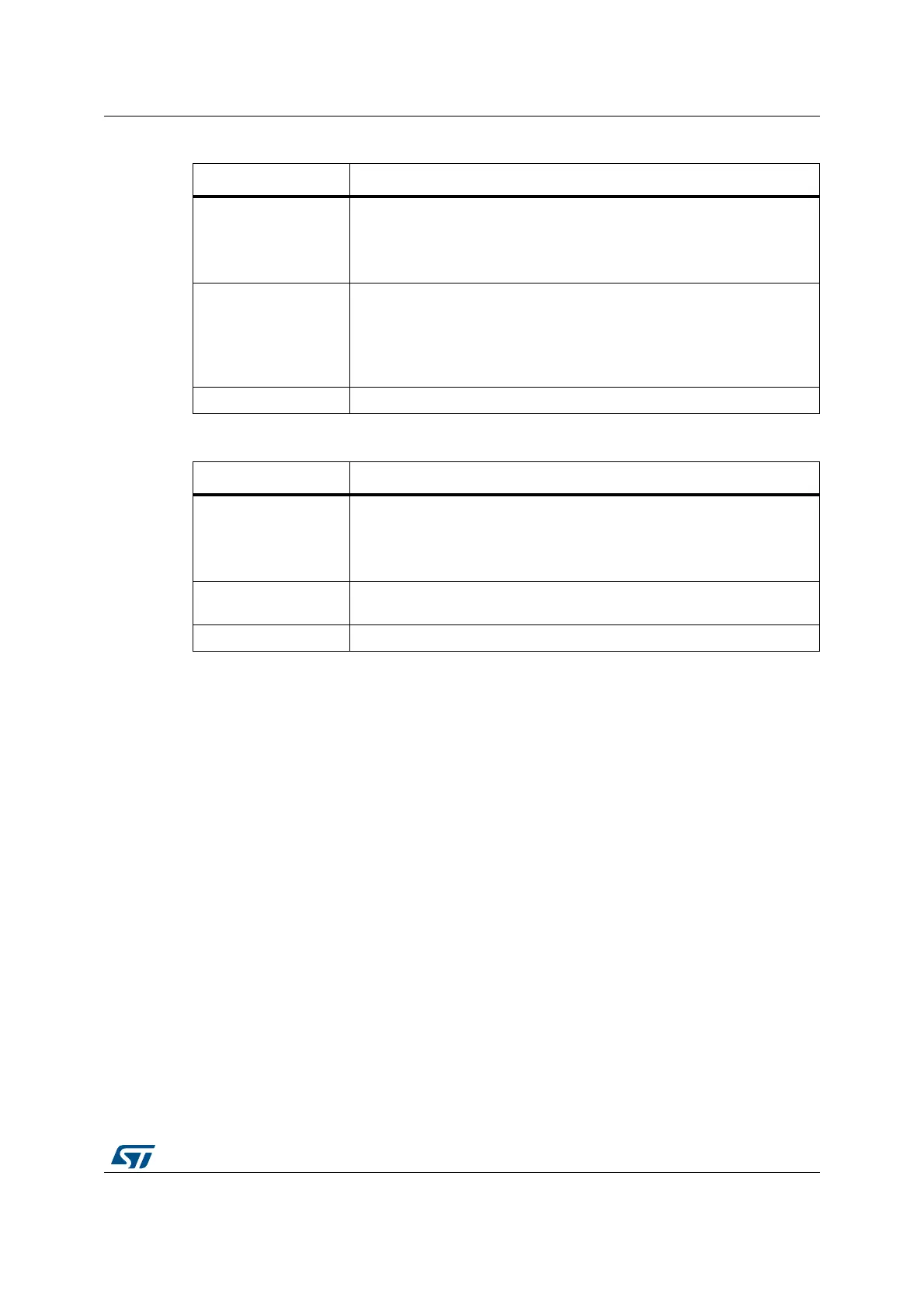

Table 12. Sleep-now

Sleep-now mode Description

Mode entry

WFI (Wait for Interrupt) or WFE (Wait for Event) while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 0

Refer to the Cortex

®

-M3 System Control register.

Mode exit

If WFI was used for entry:

Interrupt: Refer to Section 10.1.2: Interrupt and exception vectors on

page 197

If WFE was used for entry

Wakeup event: Refer to Section 10.2.3: Wakeup event management

Wakeup latency None

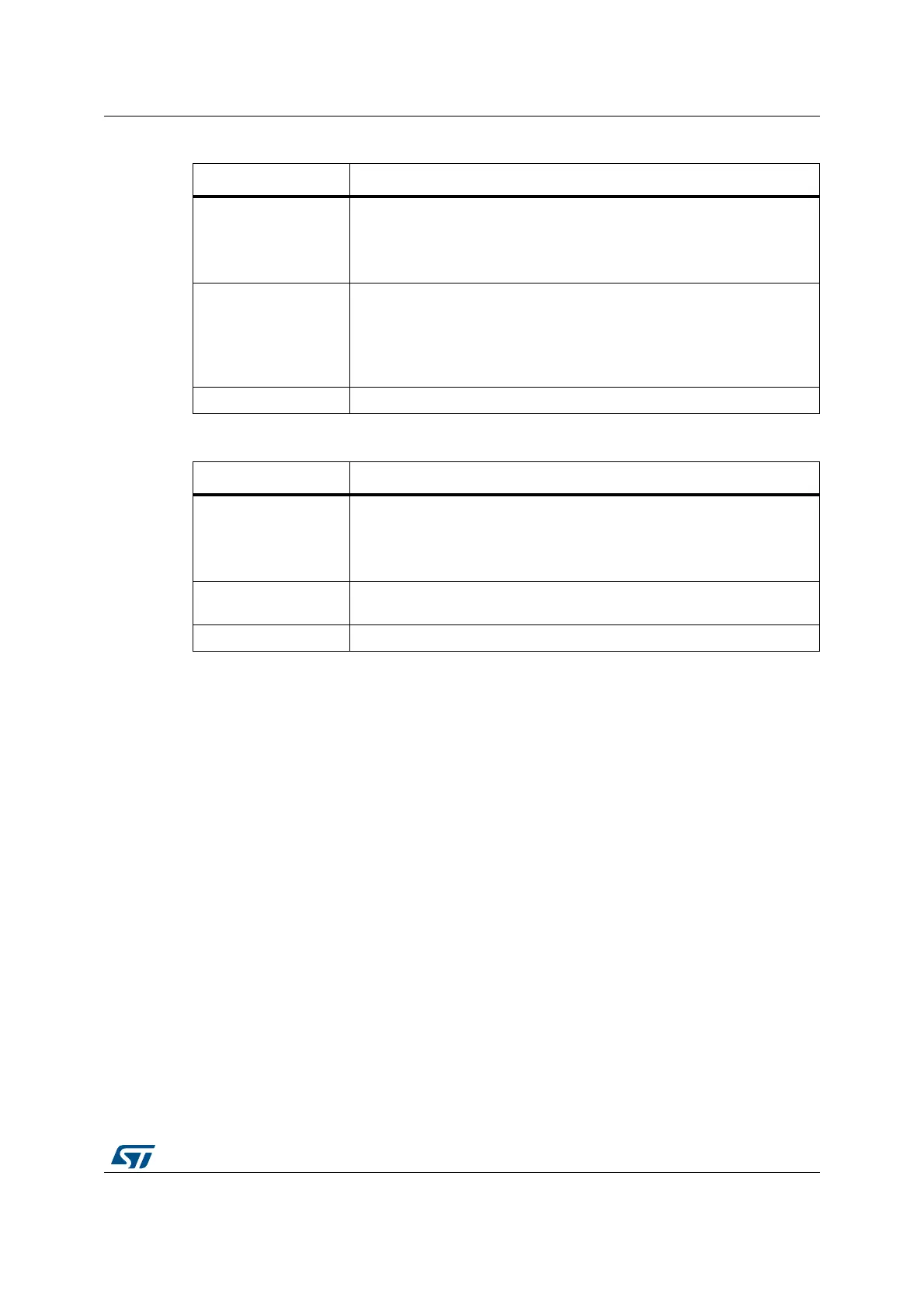

Table 13. Sleep-on-exit

Sleep-on-exit Description

Mode entry

WFI (wait for interrupt) while:

– SLEEPDEEP = 0 and

– SLEEPONEXIT = 1

Refer to the Cortex

®

-M3 System Control register.

Mode exit

Interrupt: refer to Section 10.1.2: Interrupt and exception vectors on

page 197.

Wakeup latency None

Loading...

Loading...